对设计中的组件进行例化时,仿真器必须引用描述组件功能的库才能确保正确完成仿真。

AMD 库根据模型功能分为多个类别。您必须根据仿真点指定不同仿真库。本文详细描述了 UNIMACRO 库。

当 RTL 对器件宏进行例化时,使用 UNIMACRO 库进行行为仿真。

请参阅《Vivado Design Suite 7 系列 FPGA 和 Zynq 7000 SoC 库指南》(UG953) 以获取器件宏列表。

这些宏根据宏参数设置与器件原语绑定。

因此在功能仿真中改用 UNISIM 库。

VHDL UNIMACRO 库

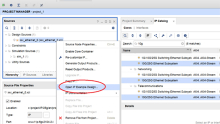

VHDL UNIMACRO 库位于

要使用这些宏,请将以下两行内容置于每个文件开头:

library UNIMACRO; use UNIMACRO.Vcomponents.all;

您还必须编译该库,并将其映射到仿真器。

方法取决于仿真器。

Verilog UNIMACRO 库

Verilog UNIMACRO 库位于

在 Verilog 中,在独立 HDL 文件内指定各库模块。

这样即可允许 -y 库规范开关为所有组件搜索指定的目录,并自动扩展该库。

不同于 VHDL 中的要求,使用模块之前,无需在 HDL 文件中指定 Verilog UNIMACRO 库。

Verilog 区分大小写,请确保 UNIMACRO 宏例化遵循大写命名约定,例如,BRAM_TDP_MACRO。

如果使用预编译库,请使用正确的仿真器命令行开关来指向预编译的库。

Vivado 仿真器示例如下:

-L unimacro_ver -L unisims_ver

由于 UNIMACRO 模型会例化底层 UNISIM 模型,因此也会指向 UNISIM 库。