AMD 推出 Spartan UltraScale+ 系列,专为成本敏感型边缘应用打造

judy 在 周三, 03/06/2024 - 11:46 提交

Spartan UltraScale+ 器件能为边缘端各种 I/O 密集型应用提供成本效益与高能效性能

Spartan UltraScale+ 器件能为边缘端各种 I/O 密集型应用提供成本效益与高能效性能

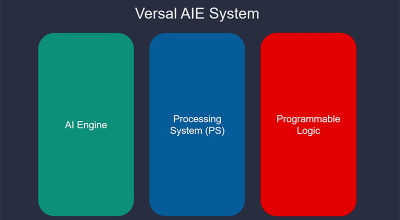

本文介绍如何在Versal器件中推迟XilSEM的扫描工作

在本电子书中,您将了解到电机的发展演变,以及可以通过电机控制来处理的性能参数

Zynq UltraScale+ MPSoC 有助于解决嵌入式 NDI 编解码器的技术、成本、功耗和其它挑战。

采用相同工具输入的情况下,Vivado 结果是否可重复?

在文中,我们将构建系统、分析生成的输出并在硬件仿真中使用 QEMU 运行系统。

AMD 为广播及专业多媒体系统提供了广泛的硬件平台。无论是 FPGA、自适应 SoC

展示包括“5G 先进性”和“6G 与 AI”在内的众多演示

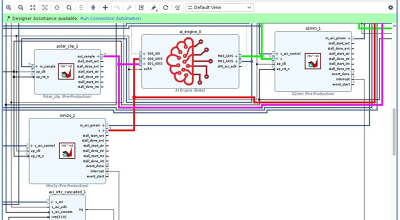

本文将演示在这 3 个不同域上运行的完整系统示例

本文让广大 AI 开发者进一步地了解如何使用 KRIA KR260 机器人入门套件开发机器人 AI