基于Vitis-AI的车牌识别系统

judy 在 周三, 11/09/2022 - 10:21 提交

Vitis-AI提供了大量的预构建模型。这个项目描述了如何利用这些模型来实现车牌识别。

Vitis-AI提供了大量的预构建模型。这个项目描述了如何利用这些模型来实现车牌识别。

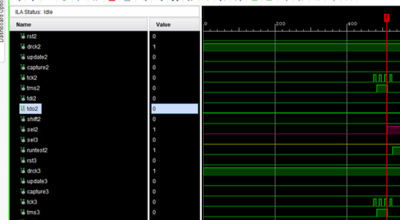

本文对如何在一个工程里例化和使用多个BSCANE2模块做一个简单说明

本文描述了一个使用专用高速收发器的多级串行接口。该设计以非整数数据恢复单元为基础,将数据速率下限扩展到0 Mb/s。

本视频主要展示如何使用 AMD Xilinx Vitis AI 自定义 OP 流程执行用户定义 AI 模型。

PetaLinux工程会自动下载代码并编译。很多时候,工程师需要修改代码,加入调试信息

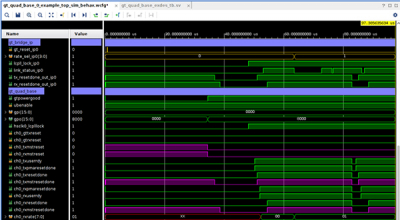

演示:使用 Jupyter Notebook 运行结构调试示例。

本篇博文侧重于提供 Versal™ GTY 仿真示例、演示 GTY 如何解复位以及如何执行速率变更。

Vitis™ 统一软件平台 2022.2 版已正式发布!主要增强特性包括下列内容

演示:在 Jupyter Notebook 中运行 IBERT 示例。

AMD XILINX 近期全新推出了 Vivado® ML Editions 2022.2 版给工具集带来了多项重大改进与增强功能。