FIFO读数据异常分析

judy 在 周二, 05/10/2022 - 09:44 提交

FIFO是FPGA设计中最常用的IP,读写时序相对简单,可能正是因为这个原因,通常不会去细读FIFO手册,具体怎么操作大概清楚,上手就写,一般不会出什么问题。最近却遇到读FIFO异常的情况,特意记录一下

FIFO是FPGA设计中最常用的IP,读写时序相对简单,可能正是因为这个原因,通常不会去细读FIFO手册,具体怎么操作大概清楚,上手就写,一般不会出什么问题。最近却遇到读FIFO异常的情况,特意记录一下

FIFO最常被用来解决写、读不匹配的问题(时钟、位宽),总结下来,其实FIFO最大的作用就是缓冲。既然是缓冲,那么就要知道这个缓存的空间到底需要多大。

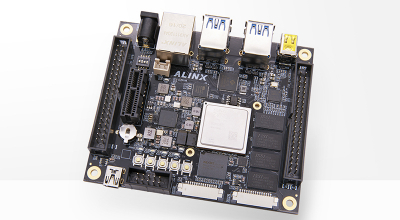

FIFO是FPGA应用当中非常重要的模块,广泛用于数据的缓存,跨时钟域数据处理等。学好FIFO是FPGA的关键,灵活运用好FIFO是一个FPGA工程师必备的技能。本章主要介绍利用XILINX提供的FIFO IP进行读写测试。

单口与双口的区别在于,单口只有一组数据线与地址线,因此读写不能同时进行;而双口有两组数据线与地址线,读写可同时进行;FIFO读写可同时进行,可以看作是双口;

前3篇咱们介绍了 SelectIO 逻辑资源,本篇咱们就聊一聊与SelectIO 逻辑资源水乳交融、相得益彰的另一个概念——IO_FIFO。1个IO_FIFO包括1个IN_FIFO 和1个OUT_FIFO,它是7系列FPGA新设计的IO专用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)逻辑功能的扩展。

作者:Kevin Zhang

本篇文章整理一下同步FIFO的实现。首先介绍一下FIFO的基础知识: