开发者分享 | 如何在Vitis中把设置信息传递到底层的Vivado (下)

judy 在 周五, 07/30/2021 - 10:45 提交

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado。

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado。

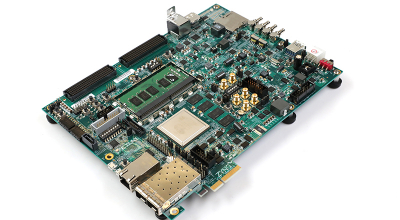

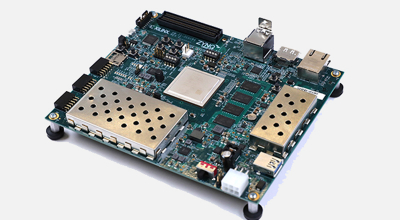

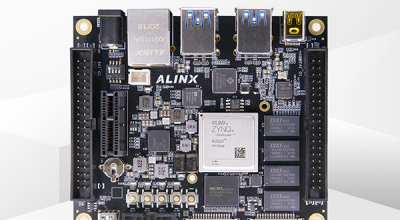

上一篇文章讲到了如何生成可供Vitis使用的XRT platform。这次我们使用生成的platform来开发一个完整的加速器Demo并在ZCU06上跑通。

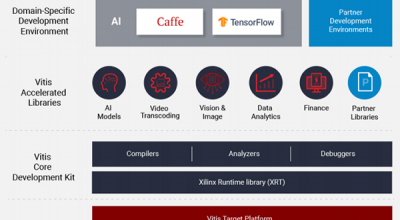

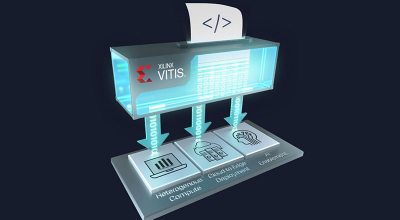

毕设要用到Xilinx家的ZCU106这块板子,了解到最近Xilinx统一了Vivado,XilinxSDK,并集成了常用开源IP核,推出了Vitis统一软件平台,使我们不再需要关注底层的Verilog实现,因此尝试使用Vitis开发一个神经网络加速器,作为毕设的基础。

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析时序问题的原因, 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivado各个步骤的选项做不同方向的优化。

Vitis + ZCU104案例教程分享

Vitis 加速基本平台创建

8月3日-12日,赛灵思软件与 AI 专家团特举办四期系列线上公开课,深入探讨如何在调整部署平台架构,满足应用不断增长的挑战与其独特需求的同时,一如既往地使用 TensorFlow 和 Caffe 等高层次框架,采用 C、C++ 和 Python 等熟悉的编程语言进行开发。

本期视频邀请到赛灵思高级产品应用工程师陈雯,将介绍 Github 上开源的 Vitis 视频加速库的相关内容,并演示在Avleo U50 的板卡上,从Vitis IDE 中调用Vitis™视觉库的加速内核的应用实例解析。

在 Github 上探索 60 多个综合性 Vitis 教程,涵盖硬件加速器、运行时和系统优化、机器学习等

在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel时,系统会自动为Kernel的时钟设置默认频率。以 xilinx_u200_qdma_201910_1 平台为例,在Vitis中选择平台时可以看到默认的时钟频率是300Mhz和500Mhz。