在 Windows 10 上创建并运行 AMD Vitis™ 视觉库示例

judy 在 周三, 05/08/2024 - 10:08 提交

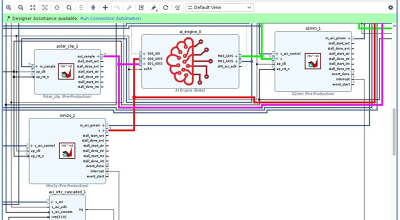

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。

在使用Vitis开发时,当硬件设计发生变化时,这时就需要更新xsa文件。

独立的Vitis嵌入式安装程序提供简单的工具安装,下载量减至大约10GB,安装量减至大约15GB

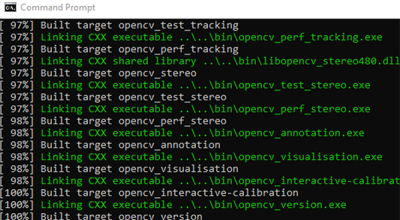

本文主要介绍OpenCV在Windows 10上的安装和设置。

Vitis Unified IDE使用“System Device Tree (SDT)”将硬件元数据从Vivado传递到 Vitis

在 2023.2 版的全新 Vitis Unified IDE 中,不再生成 DeviceID 作为索引参数用于独立 BSP 驱动程序内的

在文中,我们将构建系统、分析生成的输出并在硬件仿真中使用 QEMU 运行系统。

最近工作用petalinux编译出的镜像无法满足当下工作的需要,故想着换一条思路用Vitis进行裸机开发

Vitis 统一软件平台可实现在Xilinx异构平台上开发嵌入式软件和加速应用

HLS代码编写好之后,需要手动进行build编译