SDSoC+ DVFS on ZC702

judy 在 周四, 05/30/2019 - 09:25 提交

该项目用2018.2版Vivado, SDSoC, Petalinux搭建,只适用于2018.2版本!

搭建环境:

Windows10: Vivado2018.2, SDSoC2018.2(也可以在Ubuntu16.04完成)

Ubuntu16.04: Petalinux2018.2

PYNQ-Z1/Z2, v2.1 img

该项目用2018.2版Vivado, SDSoC, Petalinux搭建,只适用于2018.2版本!

搭建环境:

Windows10: Vivado2018.2, SDSoC2018.2(也可以在Ubuntu16.04完成)

Ubuntu16.04: Petalinux2018.2

PYNQ-Z1/Z2, v2.1 img

在本系列视频中,我们将了解如何将三重缓存模式下设置的 AXI VDMA IP 集成到 Vivado 设计的视频流水中。该设计将针对使用 PS DDR 的 Zynq®-7000 SoC ZC702 评估套件来进行设计。

在上一个视频系列中(编号 21)中,我们创建了一种设计,可将模式(使用的是 LogiCORE™ IP 视频测试模式生成器 (TPG) 的核)发送到 Zynq®-7000 SoC ZC702 评估套件的板载 HDMI 中。在本视频系列中,我们来了解一下如何修改硬件设计和应用以支持多种视频分辨率。

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

前面我们介绍了按键中断,其实我们稍作修改就可以用按键控制LED了。做个小实验,两个按键分别控制两个led亮灭。

板子:zc702。

硬件部分

添加zynq核:

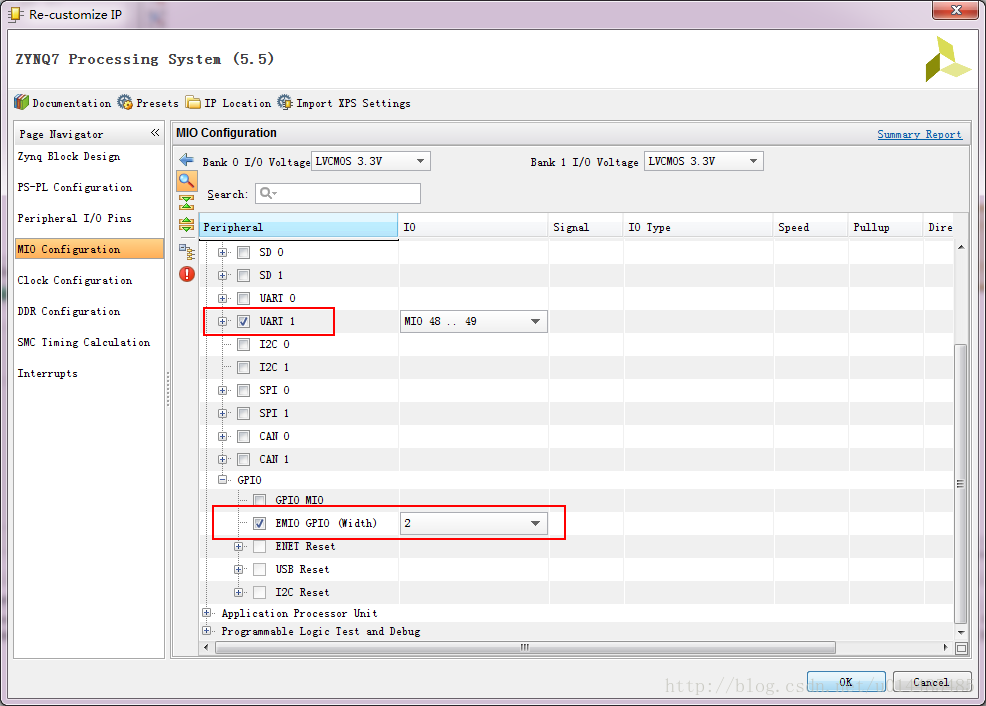

勾选串口用于打印信息,勾选EMIO,我们控制两个led,所以需要2bit

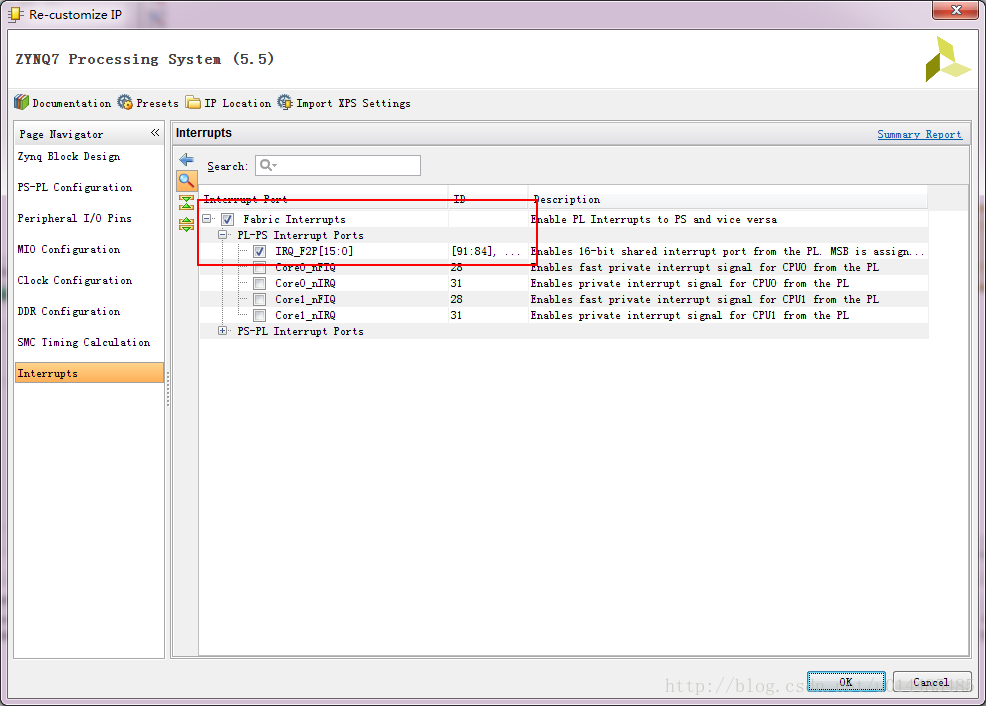

PL 到PS的中断勾选上:

PL时钟什么的都用不到,我们用的按键不需要时钟,EMIO属于PS。

再添加一个concat IP用于合并两路按键信号:

PS和PL之间的交互,怎么都逃不过中断,稍微大型的数字系统,PS和PL之间配合使用就需要中断作为桥梁。本文通过按键发起中断请求尝试学习PL请求中断的处理机制。

上一节我们观察了AXI总线的信号,了解了基于AXI总线读写的时序,这一节我们继续探索基于AXI总线的设计,来看一看ZYNQ系列开发板的独特优势,PS可以控制PL产生定制化的行为,而不需要去动硬件代码。