管脚约束问题导致生成bit时报错 如何在不重新Implentation情况下生成bit?

judy 在 周二, 10/19/2021 - 10:57 提交

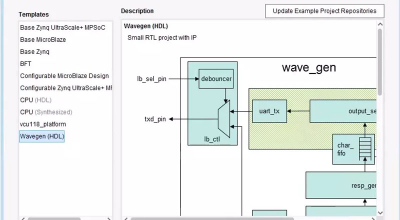

在FPGA开发中,我们经常遇到因为管脚忘记约束,导致最后生成bit的时候报错。像上面这个图中,由于在约束中忘记指定mdc和mdio的电平,再经过了长时间的综合和实现后,最后的Generate Bitstream报错了。这种情况下,如何才能不重新Implementation的情况下生成bit呢?

在FPGA开发中,我们经常遇到因为管脚忘记约束,导致最后生成bit的时候报错。像上面这个图中,由于在约束中忘记指定mdc和mdio的电平,再经过了长时间的综合和实现后,最后的Generate Bitstream报错了。这种情况下,如何才能不重新Implementation的情况下生成bit呢?

本篇文章我们以Vivado的wave_gen工程为例,来看下如何通过ECO来增加一个LUT,并对内部信号实现取反的功能。

ECO 指的是 Engineering Change Order ,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 是从 IC 设计领域继承而来,Vivado上 的 ECO 便相当于 ISE 上的 FPGA Editor。