【工程师分享】扩展MPSoC中断

judy 在 周四, 04/29/2021 - 16:06 提交

MPSoC是带ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请参考文档APU GIC: CoreLink GIC-400 Generic Interrupt Controller, DDI 0471B, r0p1。

MPSoC是带ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请参考文档APU GIC: CoreLink GIC-400 Generic Interrupt Controller, DDI 0471B, r0p1。

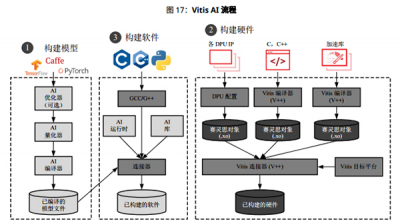

本演示概述了智能相机应用,并指导用户如何设置环境、运行加速应用以及从应用自定义 AI 模型以及生成基准测试数据。

随着第三次人工智能浪潮的到来,AI正以前所未有的速度覆盖生产和管理等领域,市场对AI推断的效率与易用性都提出了更高的要求。赛灵思通过 Vitis AI和自适应计算加速平台充分发掘AI 加速潜能并将底层 FPGA 和 ACAP 的繁复细节抽象化,帮助缺乏专业知识的用户轻松开发深度学习推断应用,再度刷新AI推断的高效性和易用性。

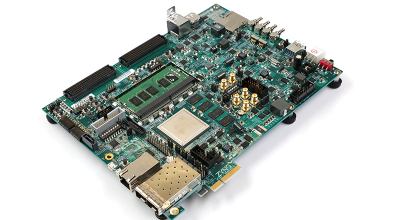

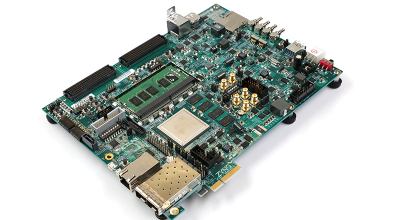

本电子书重点介绍了Xilinx Zync® UltraScale+™ RFSoC,一个可扩展至完全支持6GHz以下频段的单芯片自适应无线电平台。此高性能RFSoC支持雷达、5G和卫星通信等RF无线解决方案所需的低功耗、高性能等特性。Zynq UltraScale+ RFSoC ZCU111评估套件旨在评估UltraScale+ ZCU28DR器件,并提供全面的射频模数信号链原型平台。

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

详细了解 Kria KV260 Vision AI 入门套件和随附的基本配件包。我们将向您展示在没有 FPGA 经验的情况下,如何快速、轻松地启动并运行我们的智能相机加速应用。

本视频将带您了解全新 Kria K26 SOM。专为加速视觉 AI 应用而构建,生产就绪型 K26 是在边缘部署自适应硬件的最快方法。Kria SOM 在设计时就考虑了软件工程师的需求,无需 FPGA 编程经验即可提供熟悉的设计环境,并由 KV260 低成本即用型开发工具包支持,轻松上手。

赛灵思公司今日宣布推出 Kria™ 自适应系统模块( SOM )产品组合,这款可量产化的小尺寸嵌入式板卡可在基于边缘的应用中实现快速部署。Kria 自适应 SOM 具备完整的软件堆栈与预构建的生产级加速应用

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。

在赛灵思推出的 Zynq UltraScale+ MPSoC白皮书中,详细解读了基于 InFO 封装的全新 Zynq UltraScale+ MPSoC 如何实现紧凑型工业摄像头,并全面展现了其所具备的优秀的性能、功耗比等优势。