【下载】7系列FPGA SelectIO资源 用户指南

demi 在 周一, 01/20/2020 - 10:56 提交

Xilinx®7系列FPGA包括四个FPGA系列,这些系列均设计用于最低功耗,从而使通用设计可在各个系列之间扩展以实现最佳功耗,性能和成本。

Xilinx®7系列FPGA包括四个FPGA系列,这些系列均设计用于最低功耗,从而使通用设计可在各个系列之间扩展以实现最佳功耗,性能和成本。

上一篇博文介绍了GTX的发送端,这一篇将介绍GTX的RX接收端,GTX RX接收端的结构和TX发送端类似,数据流方向相反,不过和发送端也有一些区别.....

每一个收发器拥有一个独立的发送端,发送端有PMA和PCS组成,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。

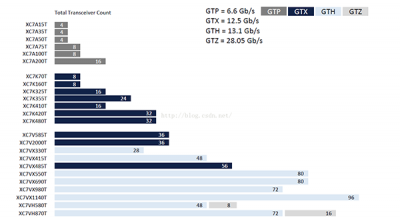

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同。

Xilinx的官方文档在介绍FPGA的逻辑资源时通常是按照CLB(Configurable Logic Block)来介绍,把CLB作为FPGA里的最小逻辑单元。但是CLB是由2个slice构成,因此平时大家都把slice挂嘴边,称为最小的逻辑单元,很少提起CLB。因此本篇咱们就简要聊一聊slice的功能。对于大部分应用,咱们不必深入了解slice,写好代码后FPGA的开发软件会自动帮助咱们布局布线,所以本篇以了解为主,当然如果您是高级用户,是大佬级FPGA专家,就另当别论。

7系列FPGA的slice包含4个部分:

(1)逻辑功能产生器,也就是咱们常说的查找表,1个slice里包含4个6输入的查找表。

(2)存储单元,也就是常说的触发器,1个slice里包含8个触发器。每4个触发器为一组,可配置成D触发器或锁存器。

(3)多路复用器,也就是1位宽的数据选择器,数量非常多,足够使用。

(4)进位逻辑,它与本列的上下slice的进位逻辑相连,实现数据运算时的进位操作。

上篇仅仅简要的介绍了时钟的用法,并未详细的说明,主要是因为很多时钟用法是针对特定的应用需求,无法一一介绍。本篇将重提上篇的CMT时钟模块,聊一聊它的用法。可以这么说,每个靠谱的FPGA应用里都应该用到CMT模块。

上一篇咱们介绍了7系列FPGA的时钟区域内部结构,本篇咱们接着介绍如何实际操作时钟。不说其它的,直接先上两张图。

上一篇咱们介绍了7系列FPGA的整体时钟架构,知道了FPGA是由很多个时钟区域组成,时钟区域之间可以通过Clock Backbone 和CMT Backbone来统一工作。本篇咱们就说一下时钟区域的内部结构。

本博文介绍了利用 POST_CRC 试错的方法,但总体而言,赛灵思推荐在所有架构上使用 Soft Error Mitigation (SEM) IP。SEM IP 提供了一种可用于测试 SEU 检测与纠正能力的机制并提供了更强大的调试能力。

本篇作为xilinx 7系列FPGA简介篇的最后一篇,咱们来介绍MGT(Multi-gigabittransceiver)