【在线免费培训】启动Xilinx AI专用平台Versal ACAP

judy 在 周三, 03/03/2021 - 14:32 提交

在活动中,您将了解最新的 xilinx Versal ACAP 平台及其组成模块,支持更灵活地实现加速系统。Versal独有的功能特性,如人工智能引擎(AIE)和片上网络(NoC),将在Vitis统一软件工具流程中覆盖支持。其主要目的是让您能将新的应用程序与Versal关联起来,并使您能够探索这个平台和工具。

Vitis 是由赛灵思(Xilinx)推出的一款开发工具套件,用于加速应用程序的开发和部署,尤其专注于基于赛灵思的可编程逻辑设备(FPGA)的加速。

Vitis 工具套件的目标是简化 FPGA 加速应用程序的开发流程,使更广泛的开发者能够充分利用 FPGA 提供的硬件加速性能,从而加速特定领域的计算任务。

在活动中,您将了解最新的 xilinx Versal ACAP 平台及其组成模块,支持更灵活地实现加速系统。Versal独有的功能特性,如人工智能引擎(AIE)和片上网络(NoC),将在Vitis统一软件工具流程中覆盖支持。其主要目的是让您能将新的应用程序与Versal关联起来,并使您能够探索这个平台和工具。

3月10日与您相约蓉城, 为您带来赛灵思软件与 AI 方向面对面交流活动!本活动全程免费,名额有限。参会资格以微信审核通知为准,迅速报名吧,干货多多,礼品也多多!

本文描述了Vitis™ AI开发包,这是一个用于深度学习处理器单元(DPU)的全栈深度学习SDK。

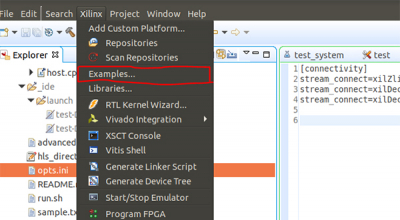

自从 Vitis 发布后,Xilinx 在 Github 上持续开源了很多资源,方便开发者进行自己的设计,减少产品上市时间。所以本期文章我们来看下如何获取和使用 Github 上的开放资源。

本视频将介绍Vitis AI 设计流程原理及Vitis AI1.3版的新功能。

本视频将介绍Vitis HLS产品以及支持从基于C语言开始对FPGA进行编程的底层技术。

本视频展示Vitis系统集成的实例演示。介绍使用Vitis统一软件平台创建并集成RTL模块以及HLS内核的简单步骤。

本视频重点介绍如何在命令行模式下将DPU 作为 HLS 内核与 Vitis 2020.2 和 Vitis AI 1.3 集成。

通过介绍构建硬件组件、自定义软件组件以及创建 Vitis 和 Vitis AI 就绪平台的要求和步骤,专注于如何在自定义嵌入式平台上启用 Vitis AI。

在 1月19日 的线上研讨会上,我们将邀请赛灵思软件与 AI 部门的专家与大家分享集成了 AI 引擎的 Versal AI Core 器件与 CPU/ GPU / FPGA 的算力比拼;Versal AI Core 在自动驾驶、机器学习、智慧医疗等领域的实际案例;另外,还有最新发布的 Vitis 1.3 的十大亮点功能的分享和探讨。干货满满,不容错过。