HDL Verifier 通过 UVM 支持加快 FPGA/ASIC 验证速度

judy 在 周四, 03/12/2020 - 09:47 提交

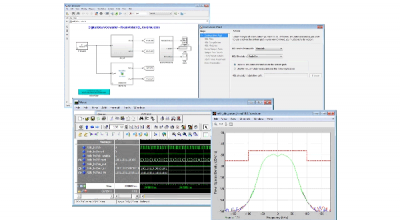

HDL Verifier 能够让开发 FPGA 和 ASIC 设计的设计验证工程师直接从 Simulink 模型生成 UVM 组件和测试平台,并在支持 UVM 的仿真器(比如来自 Synopsys、Cadence 和 Mentor 的仿真器)中使用这些组件和测试平台

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

HDL Verifier 能够让开发 FPGA 和 ASIC 设计的设计验证工程师直接从 Simulink 模型生成 UVM 组件和测试平台,并在支持 UVM 的仿真器(比如来自 Synopsys、Cadence 和 Mentor 的仿真器)中使用这些组件和测试平台

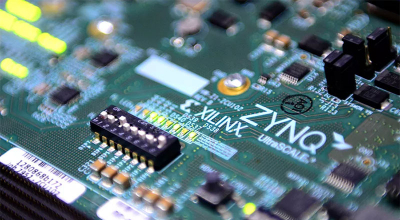

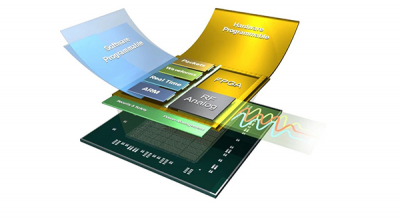

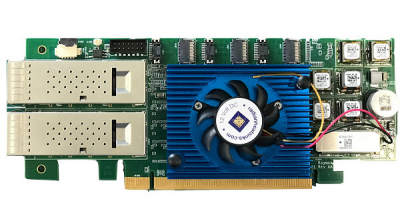

今天上午,FPGA发领头羊赛灵思公司以在线发布形式宣布推出 Versal ACAP 产品组合第三大产品系列—— Versal™ Premium,这款FPGA堪称是史上最强大FPGA,它有高度集成且功耗优化的网络硬核,是业界带宽最高、计算密度最高的自适应平台

最近有朋友问,公众号为什么起名叫网络交换FPGA?今天这篇文章就来回答一下。我们将从网络交换的历史讲起,也正如机器学习也赶上了ASIC工艺发展才引起革命性的变化一样。技术发展的历程中,总有那些看似不相关的技术结合起来,结果导致翻天覆地的变化

关键内容提要:

(1) FPGA IO命名方式;

(2) FPGA的上电时序

今天想和大家一起聊聊FPGA的IO。

在进行加减乘除运算时一定要注意位宽,保证足够大的位宽,防止数据溢出,如果溢出结果就会出现错误,尤其是加和乘运算,一定要计算好位宽(位宽的计算可以都取其最大值,看最大值计算后的位宽就是最大位宽,采用这个位宽数据就溢出不了)

FPGA开发中,一种最常用的复位技术就是“异步复位同步释放”,这个技术比较难以理解,很多资料对其说得并不透彻,没有讲到本质,但是它又很重要,所以对它必须理解,这里给出我的看法。

金融科技英译为 Fintech, 是 Financial Technology 的缩写,指通过利用各类科技手段创新传统金融行业所提供的产品和服务,提升效率并有效降低运营成本。近年来,众多金融技术公司相继推出基于 FPGA 的产品,在模型计算、高频交易等领域大放异彩。

我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

以物联网、5G 为核心特征的数字化浪潮正席卷全球,由此带来的车联网、工业物联网、人工智能生物识别带来的海量异构化数据,以及高带宽、低时延等新业务个性化需求,让传统的通用服务器及存储架构不堪重负。

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。