基于 FPGA 硬件设计DDS的跳频信号产生系统

demi 在 周一, 02/03/2020 - 16:24 提交

跳频通信具有良好的抗干扰、抗多径衰落、抗截获等能力和同步迅速等特点,广泛应用于军事、交通、商业等各个领域。其关键技术主要有三点:跳频序列发生器、跳频频率合成器和跳频同步器。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

跳频通信具有良好的抗干扰、抗多径衰落、抗截获等能力和同步迅速等特点,广泛应用于军事、交通、商业等各个领域。其关键技术主要有三点:跳频序列发生器、跳频频率合成器和跳频同步器。

① 滤波电容的放置要与电源接近,振荡器也是,在振荡器前端放电阻。② 通过Design的Board Shape改变电路板大小。

SPI——串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM、FLASH、实时时钟,AD转换器以及数字信号处理器和数字信号解码器之间。SPI是一种高速,全双工,同步的通信总线,在芯片上只占用四根线(CS、MOSI、MISO、SCK),极大的节约了芯片的引脚。

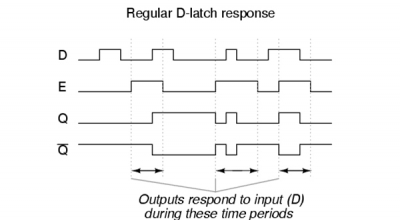

在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数文章都对锁存器有个误解,我们后面会详细说明。

在前面的章节中,我们用了很多Tcl的指令,但有些指令并没有把所有的参数多列出来解释,这一节,我们就把约束中的Tcl指令详细讲一下。

FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。现在的FPGA不仅包含以前的LE,RAM也更大更快更灵活,管教IOB也更加的复杂,支持的IO类型也更多,而且内部还集成了一些特殊功能单元......

在FPGA中我们写的最大的逻辑是什么?相信对大部分朋友来说应该是计数器,从最初板卡的测试时我们会闪烁LED,到复杂的AXI总线中产生地址或者last等信号,都会用到计数器,使用计数器那必然会用到进位链。

FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

多周期路径,我们一般按照以下4个步骤来约束:带有使能的数据;两个有数据交互的时钟之间存在相位差;存在快时钟到慢时钟的路径;存在慢时钟到快时钟的路径。