如何提高FPGA的运行速度

demi 在 周二, 11/26/2019 - 18:15 提交

对于设计者来说,当然希望我们设计的电路的工作频率尽量高。我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

对于设计者来说,当然希望我们设计的电路的工作频率尽量高。我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。

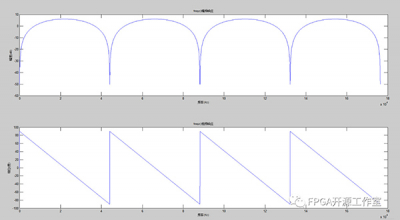

在《基于FPGA的多级CIC滤波器实现四倍抽取一》和《基于FPGA的多级CIC滤波器实现四倍抽取二》中我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理以及它们的幅频响应。此篇我们将用verilog实现基于FPGA的多级CIC滤波器实现四倍插值。

图像直方图用来反映一副图像的像素分布。其中,横坐标表示图像像素的灰度级,纵坐标表示每个灰度级对应的像素总数或占所有像素个数的百分比。

在《基于FPGA的多级CIC滤波器实现四倍抽取一》和《基于FPGA的多级CIC滤波器实现四倍抽取二》中我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理以及它们的幅频响应。在三中我们将用verilog实现基于FPGA的多级CIC滤波器实现四倍抽取。

忠告一:如果时序差的不多,在1NS以内,可以通过修改综合,布局布线选项来搞定,如果差的多,就得动代码。

在实现多级CIC滤波器前我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理。CIC滤波器在通信信号处理中有着重要的应用。

滤波是一个邻域操作算子。通常,邻域选择3x3,5x5等,这些3x3或者5x5的邻域,被称作滤波器,掩模或核。利用给定像素邻域内的像素值与掩模做卷积,从而决定该像素的最终输出值。

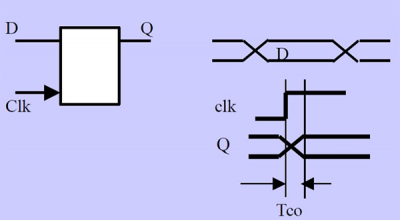

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种很简单的解读办法,可以看透它的本质,而且不需要再记复杂的公式了。

传播延时,即I/O管脚输入到非寄存器输出延时。信号从任何一个I/O脚输入,通过一个宏单元内的组合逻辑后,从另一个管脚输出,所需要的时间。范围:5~12ns。

一般基于FPGA的网络加速设计都会强调模型被压缩了多少以及FPGA上可以跑得多快,却很少集中于去改善精度。