FPGA设计规范之Verilog编码规范

demi 在 周三, 10/16/2019 - 15:29 提交

命名规则:① 首先每个文件只包含一个module,而且module名要小写,并且与文件名保持一致;② 除parameter外,信号名全部小写,名字中的两个词之间用下划线连接,如receive_clk_b;③ 由parameter定义的常量要求全部字母大写......

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

命名规则:① 首先每个文件只包含一个module,而且module名要小写,并且与文件名保持一致;② 除parameter外,信号名全部小写,名字中的两个词之间用下划线连接,如receive_clk_b;③ 由parameter定义的常量要求全部字母大写......

FPGA是可编程芯片,因此FPGA的设计方法包括硬件设计和软件设计两部分。硬件包括FPGA芯片电路、 存储器、输入输出接口电路以及其他设备,软件即是相应的HDL程序以及最新才流行的嵌入式C程序。

在fpga工程中加入时序约束的目的: 1、给quartusii 提出时序要求; 2、quartusii 在布局布线时会尽量优先去满足给出的时序要求; 3、STA静态时序分析工具根据你提出的约束去判断时序是否满足的标准。

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。首先讲述DSS(直接频率合成法)的原理。DDS是重要的频率合成方法,在波形发生器中有极其重要的应用。DDS主要由几部分组成:a) 相位累加器;b) RAM数据读取;c) D/A转换器;d) 低通滤波器。

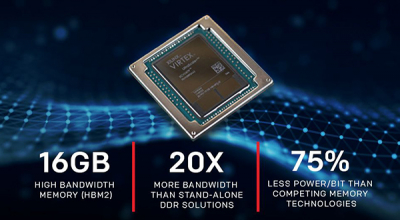

当您想到处理性能时,脑子里最先出现的影响因素往往并不是存储吧?但是,如果您正在处理大量的大型数据集,那么每个步骤的带宽都会影响到您完成工作的速度和效率。对于AI应用、8K视频处理、医疗成像、区块链和汽车解决方案等工作负载,高带宽性能带来的差异就如同玩具水枪与消防水带的区别。

在高速的同步电路设计中,时序决定了一切,要求所有时序路径都必须在约束限制的时钟周期内,这成为设计人员最大的难题,因此,首先确定和分析基本时序路径有助于设计者快速,准确地计算时序裕量,使系统稳定工作,XILINX公司提倡的几种常用基本路径。

外部触发信号到来后,执行若干步骤,步骤由计数器控制。(这里的计数器可计数为0-127)。故触发信号高电平使能计数器使能信号(用组合逻辑实现)。仅计数器记到127后,或者复位信号到来,计数器使能归0.使能一旦归零,计数器恢复0。

在当今热门的人工智能(AI)、5G、自动驾驶和超大规模数据中心应用领域,我们看到的一大市场趋势。就是越来越多的 ASIC 和 SoC 设计开始启动。在这些应用中,整个开发系统,随着新的芯片架构和集成软件不断更新换代变得越来越复杂......

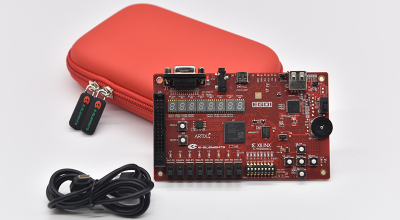

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。