《Xilinx - UG471中文翻译》(1)IDELAYE2原语介绍

judy 在 周三, 01/19/2022 - 09:10 提交

SelectIO,就是I/O接口以及I/O逻辑的总称。《UG471--SelectIO》 篇可以分成3部分:第1部分介绍I/O的电气特性,第2部分介绍I/O逻辑资源,第3部分介绍高级的I/O逻辑资源(serializer/deserializer)。

SelectIO,就是I/O接口以及I/O逻辑的总称。《UG471--SelectIO》 篇可以分成3部分:第1部分介绍I/O的电气特性,第2部分介绍I/O逻辑资源,第3部分介绍高级的I/O逻辑资源(serializer/deserializer)。

在SelectIO简介连载一中介绍了其架构,本章会继续介绍如何使用其gearbox功能来实现不同的比率的串并转换功能。7 Series FPGA中LVDS使用了ISERDESE2,SDR Rate可设为2,3,4,5,6,7,8。DDR Rate可设为4,6,8,10,14。

FPGA是电子器件中的万能芯片,Xilinx FPGA处于行业龙头地位更是非常灵活。FPGA管脚兼容性强,能跟绝大部分电子元器件直接对接。Xilinx SelectIO支持电平标准多,除MIPI C-PHY电平(三电平标准)外,IO能直接对接3.3V以及3.3V以下基本所有电平标准,初步统计支持72种不同电平标准。

本文描述Versal™设备中可用的SelectIO™资源。

Xilinx®7系列FPGA包括四个FPGA系列,这些系列均设计用于最低功耗,从而使通用设计可在各个系列之间扩展以实现最佳功耗,性能和成本。

Xilinx SelectIO IP是为了将LVDS传输过来的串行信号变为并行数据。

本篇咱们来聊一聊高级的IO逻辑资源。所谓ISERDESE2模块,即Input serial-to-parallel converters。该模块的作用就是实现高速源同步输入数据的串并转换。所谓OSERDESE2模块,即output parallel-to-serial converters。该模块的作用就是实现高速源同步输出数据的并串转换。

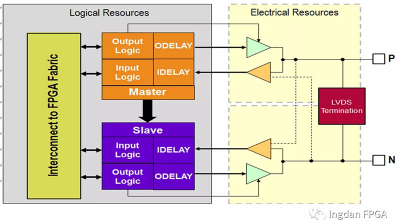

上篇咱们简单的说了I/O的电气特性,本篇咱们接着介绍I/O逻辑资源,先贴上两张图。图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

作者: 做但不能忘思考,FPGA2嵌入式

当我们使用一种新的IP核的时候,遇到的最大问题是:以前根本没有接触过的新东西,我们会感到恐惧,不知道如何下手。比如,SelectIO该怎么来实现LVDS的功能:

Step1,我们新加一个接收的SelectIO的IP核,界面如下图: