DPU Fingerprint详解

judy 在 周二, 11/21/2023 - 10:09 提交

本文将会详细介绍关于DPU Fingerprint的相关内容,并提供此类校验失败问题的检查手段和解决方案。

本文将会详细介绍关于DPU Fingerprint的相关内容,并提供此类校验失败问题的检查手段和解决方案。

Vitis AI Optimizer支持对神经网络模型进行最优化

深度学习处理器 (DPU) 是一个专为深度神经网络而优化的可编程引擎。它由一组可参数化的 IP 核组成

本文档涵盖了以下设计进程:机器学习和数据研究——将机器学习模型从 PyTorch、TensorFlow

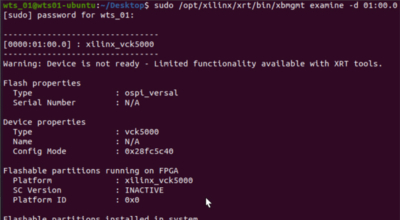

VCK5000在vitis ai 3.0对应的shell版本为xilinx-vck5000-gen4x8-qdma-base_2

本项目主要是设计AI加速器,利用Xilinx的CDMA加载权重,输入到PL区的Block Ram

本文以vitis-ai-pytorch环境为例,描述了Inspector的用法并给出示例。

Vitis-AI在边缘计算设备的AI全栈部署框架中扮演了编译器端与后端的角色,接收前端 DNN 框架训练后的网络参数IR

本篇博客记录移植yolov5模型的整个过程

Vitis-AI提供了大量的预构建模型。这个项目描述了如何利用这些模型来实现车牌识别。