版权声明:本文为博主原创文章,遵循 CC 4.0 by-sa 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_37512669/article/details/90062704

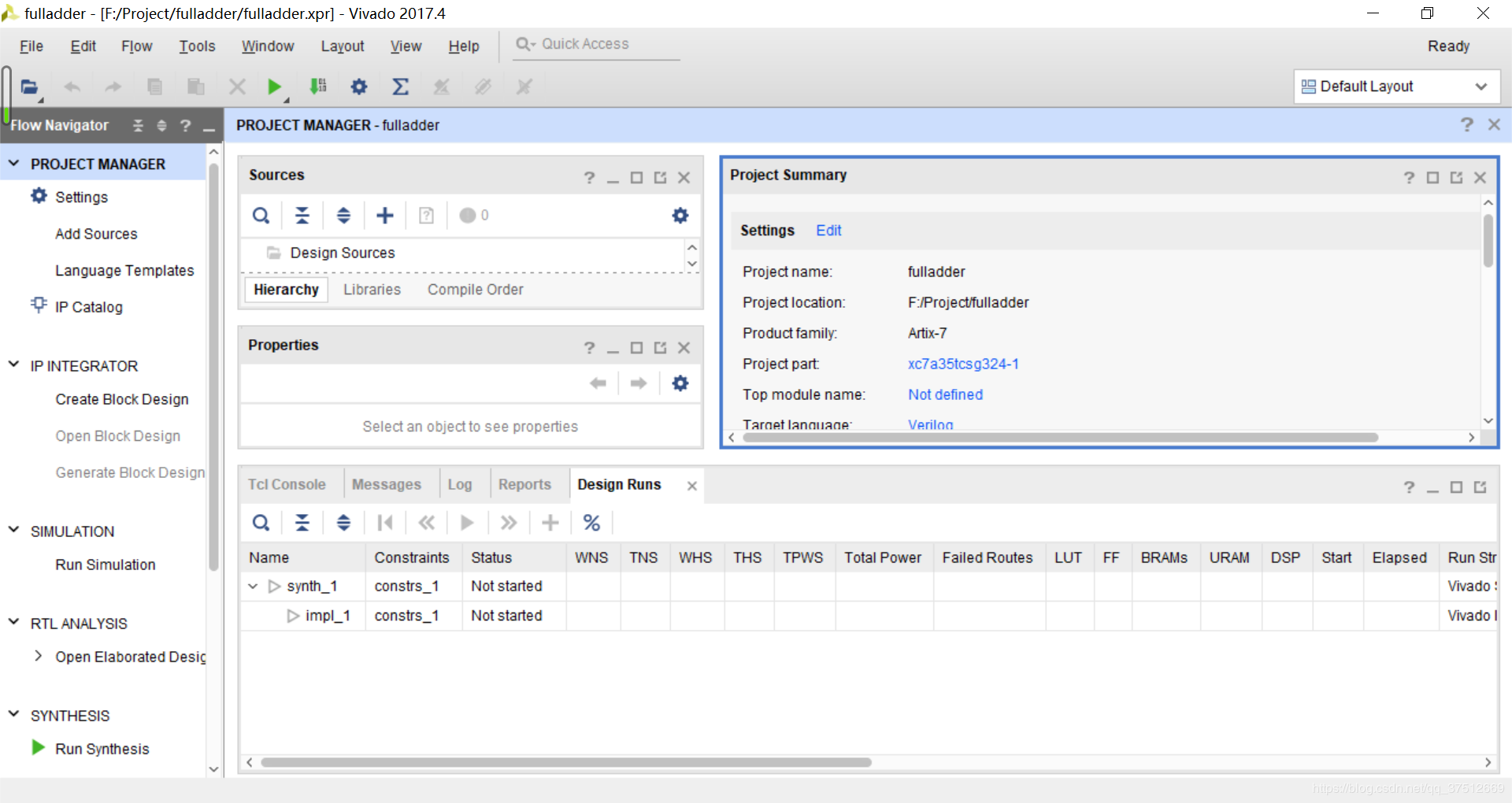

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

二、IP核应用-全加器

1、创建空白工程。

2、将上次创建的74LS00 IP核文件复制到新工程目录下。

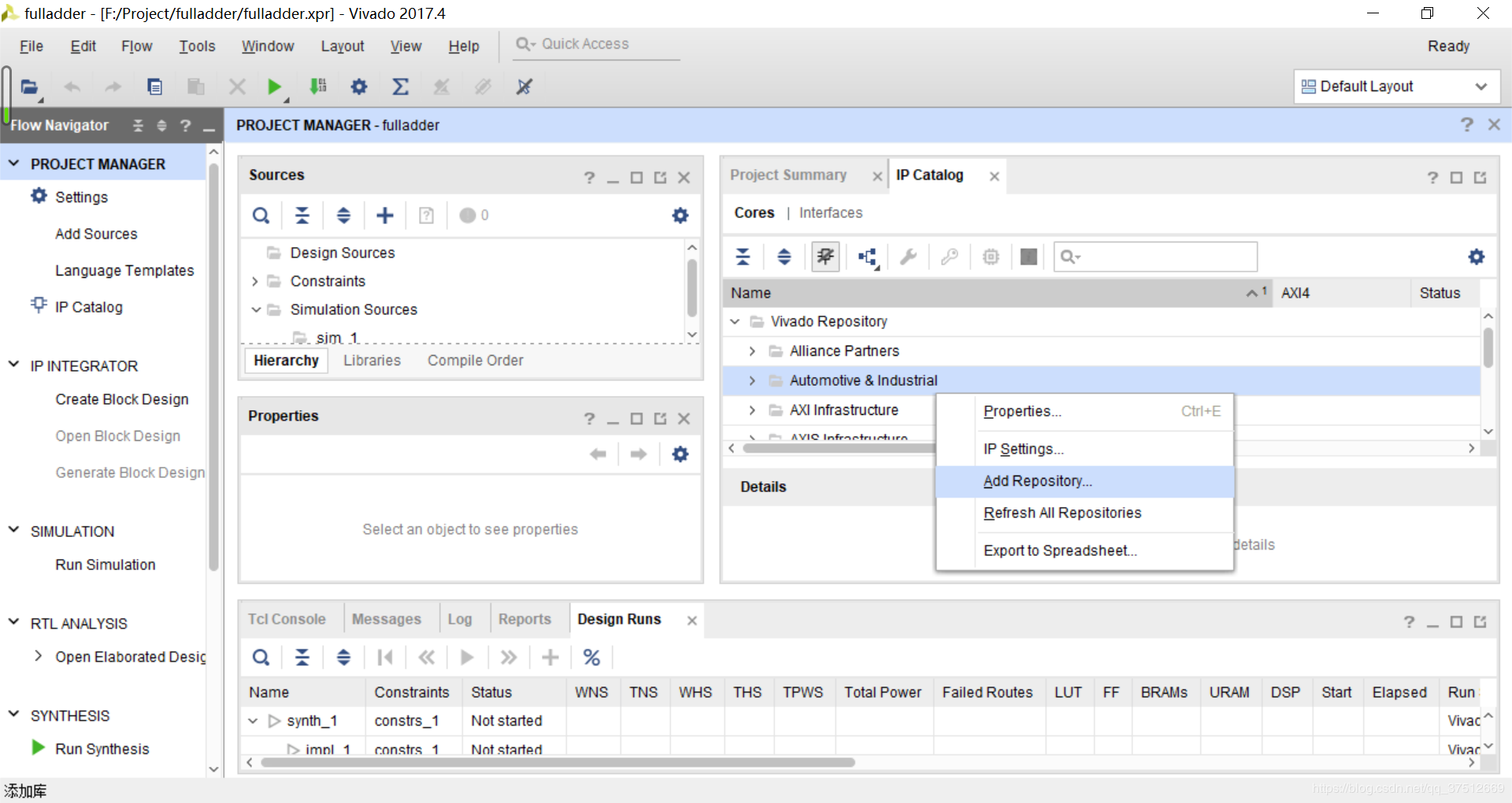

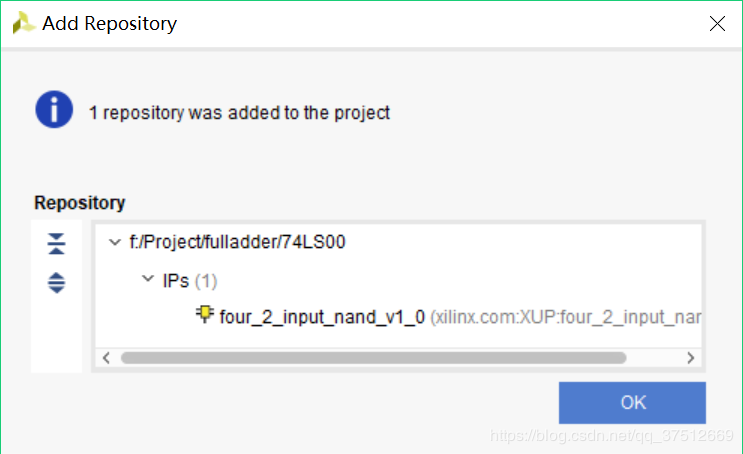

3、打开IP Catalog,右键单击选择Add Repository,添加本工程文件下的IP核目录。

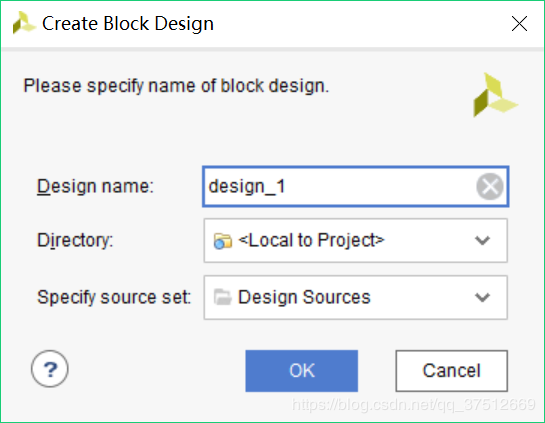

4、在IP INTEGRATOR下选择Create Block Design。创建基于IP核的原理图,保持默认设置。

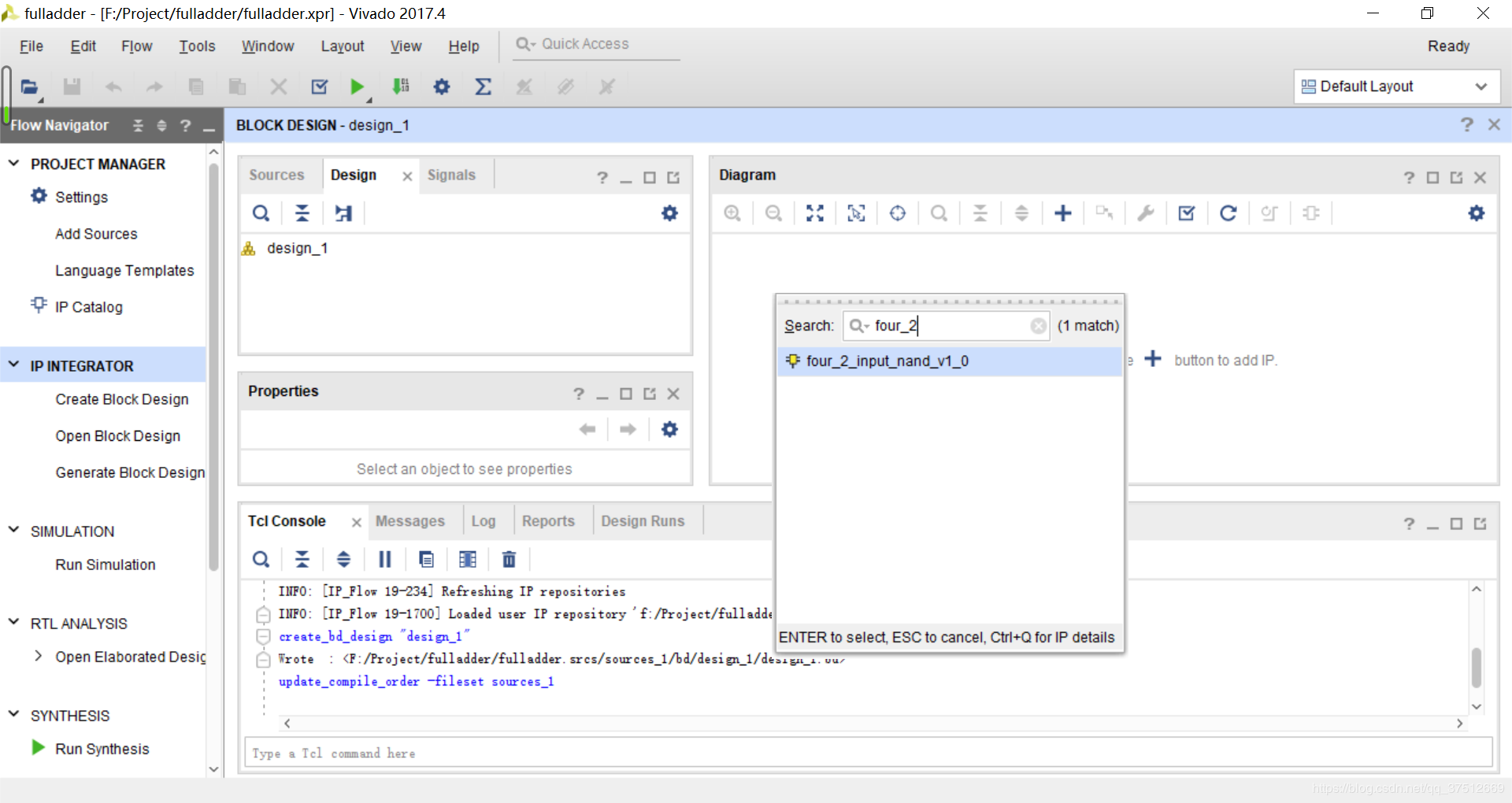

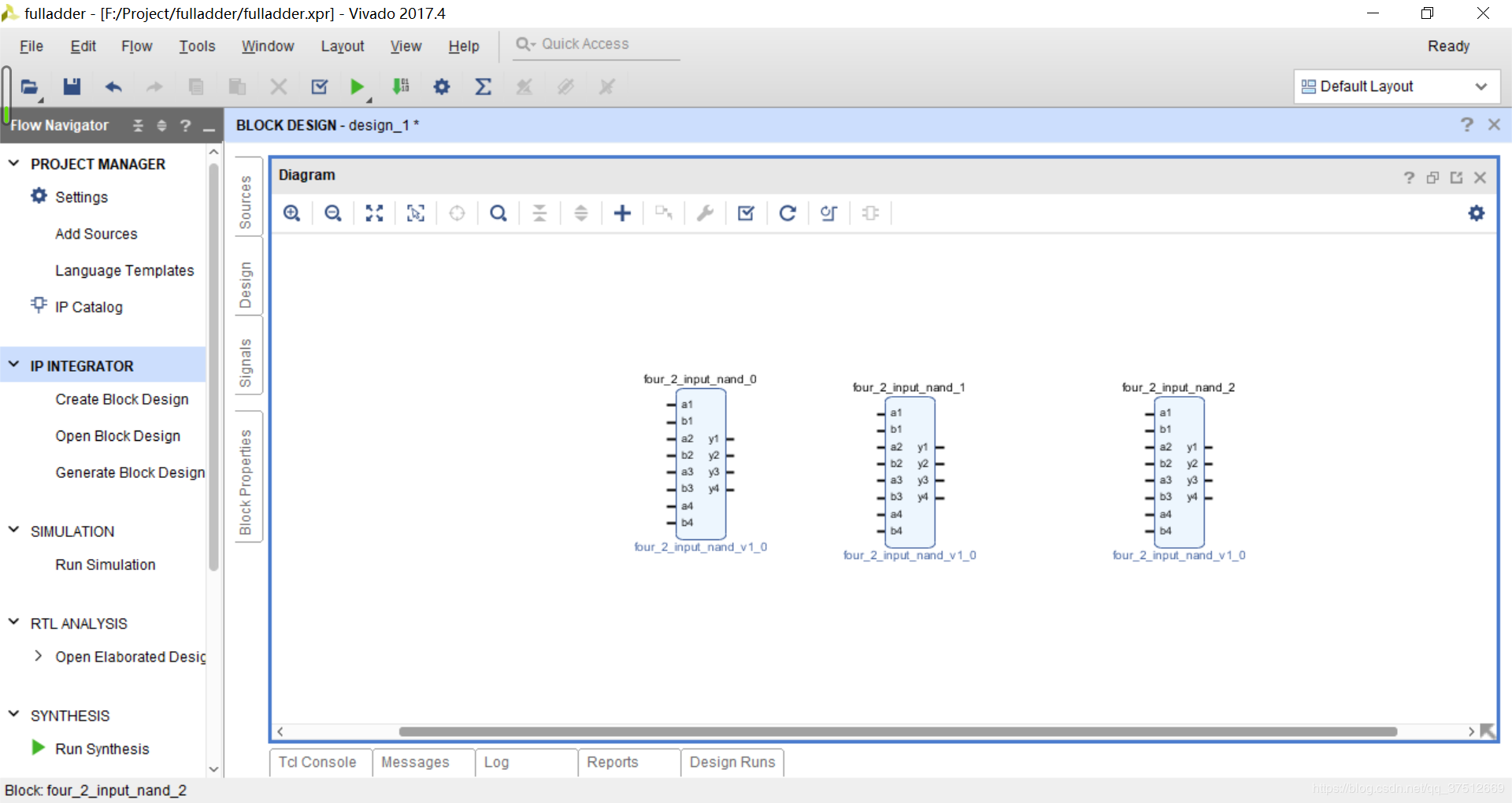

5、在原理设计图界面,添加IP核,点击+号,或者邮件Add IP,然后搜索four_2_input_nand,添加三个74LS00的核。

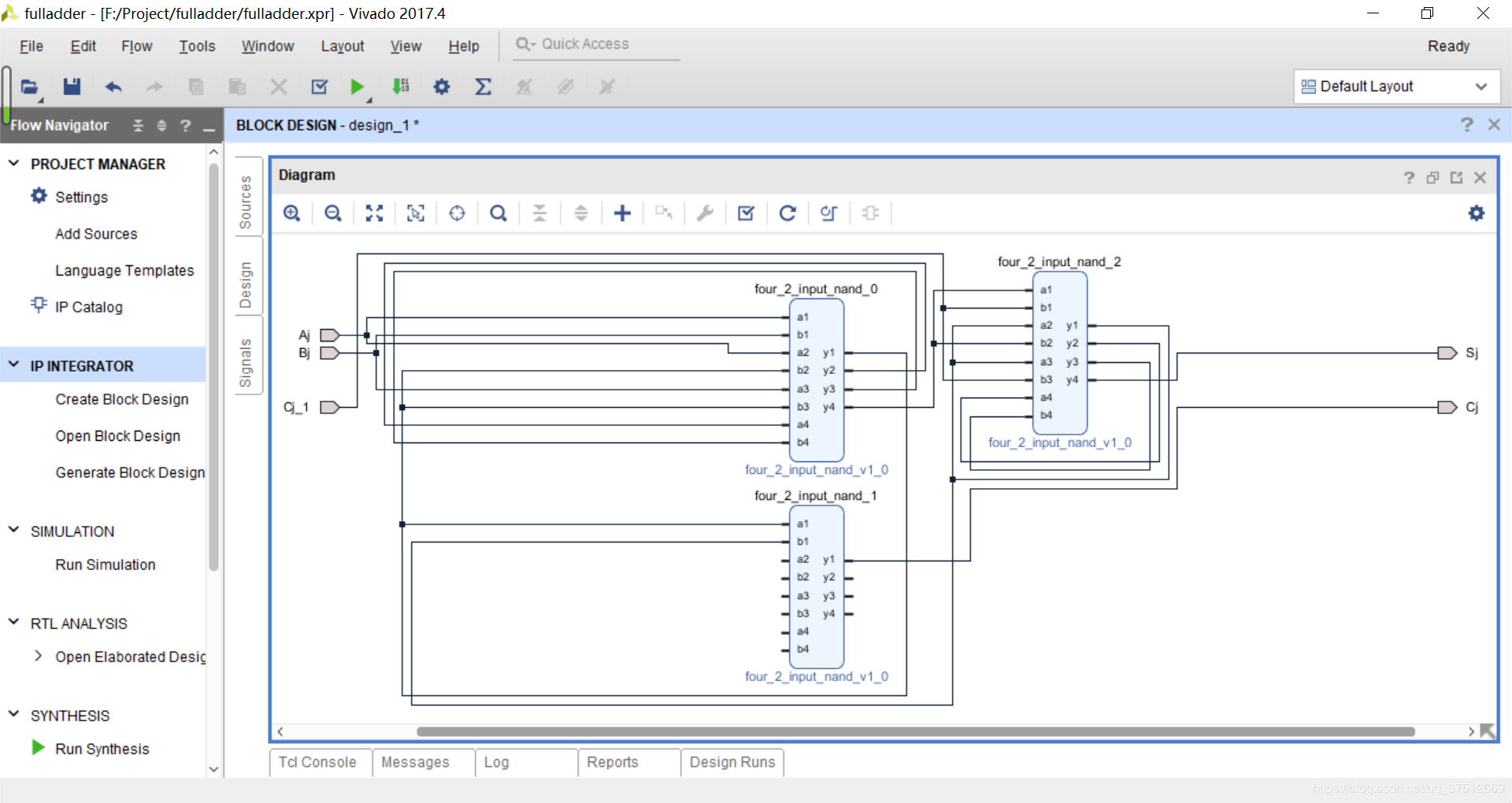

6,右键使用Create Port,创建输入输出端口,包括数据、时钟。

7、进行连线。

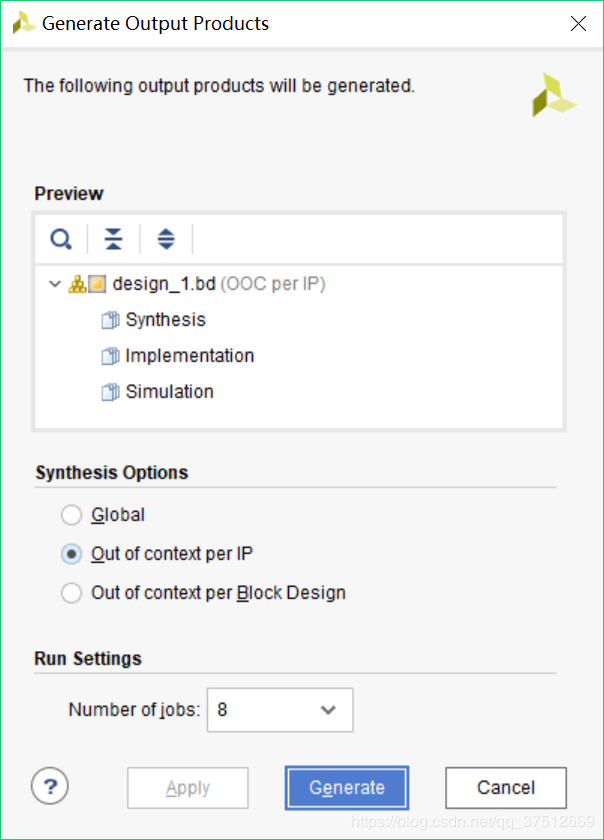

8、在工程管理器中source页面下,右键单击design_1,选择Generate Output Products,然后Generate,可能会报一部分错误,因为有部分引脚没有连接,直接OK跳过就可以。

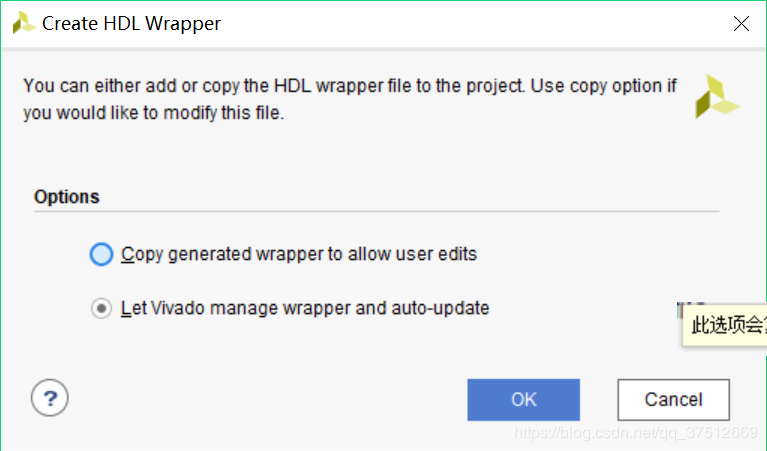

9、生成完毕后,再次右击design_1,选择Create HDL Wrapper,创建HDL代码,对原理图进行实例化,默认设置。

10、经过Run Synthesis、Run Implementation、添加约束、Generate Bitstream之后,打开Open Hardware Manager,Auto Connect,然后右键Program device。

其中SW0为加数Aj、SW1为被加数Bj、SW2为来自低位的进位Cj_1,指示灯LD2(0)作为和Sj,LD2(1)作为进位Cj。

演示视频:https://www.bilibili.com/video/av52008373/