1.目的

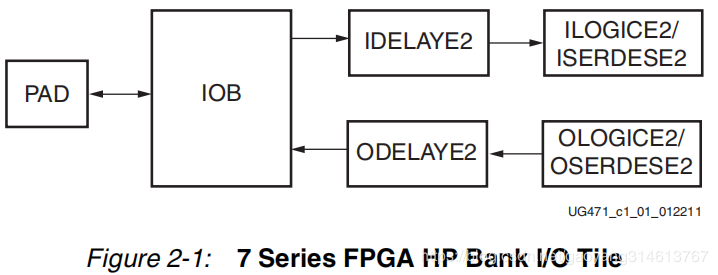

Xilinx SelectIO IP是为了将LVDS传输过来的串行信号变为并行数据。

2.原理

该IP内包含一个IDELAY和ISERDES分别是用来进行调节bit对齐和字节对齐。

3.动态相位调节(DPA)

步骤一:比特对齐

控制tap(一共可以调节32个tap,半个时钟光周期)进行相位对齐,找到数据的正中心,首先找到数据的左边界,然后找到数据的右边界,最后取这两个边界的中心就相当于数据tap的均值,使得数据稳定可以被采集。

步骤二:字节对齐

控制slip进行划位,找到训练的数据字节,保证后续数据正常。举个例子,如果发送的数据为A5,上面的比特对齐得到的数据为D2,则通过bitslip可以进行移位得到A5.具体的SDR移位和DDR移位都在UG471中可以找到。

4. 参考

https://www.xilinx.com/support/documentation/user_guides/ug471_7Series_S...

程序设计见链接:附件