1 前言

在前面的文章中ZCU106 XRT环境搭建【Xilinx Vitis】,已经生成了用于在Vitis的相关环境。

Xilinx在GitHub分享了一个Vitis的应用程序加速开发的教程:2019.2 Vitis™ Application Acceleration Development Flow Tutorials

后面基于我会基于ZCU106 XRT环境以及这个教程做一些测试。

Xilinx相关的官方文档:

https://www.xilinx.com/html_docs/xilinx2019_2/vitis_doc/kme1569523964461...

https://www.xilinx.com/html_docs/xilinx2019_2/vitis_doc/hly1569525384514...

pdf版本:

Vitis Unified Software Platform Documentation Application Acceleration Development

Vitis Unified Software Platform Documentation Embedded Software Development

2 创建Vitis工程

Tutorials中的第一个例子:Getting Started with RTL Kernels

我其实都是按照例子中的章节,并使用我生成的VCU106 XRT平台来进行测试的。

下面我仅针对需要注意的地方进行描述,相同的步骤参考文档即可。

2.1 Create an Vitis IDE Project

目的:

用于创建一个Vitis工程。

区别:

platform需要选择之前生成的zcu106vcu_base

2.2 Configuration with the RTL Kernel Wizard

目的:

通过Vivado的RTL Kernel Wizard生成一个自定义RTL Kernel Template

区别:

无

2.2.1 RTL Kernel说明

RTL Kernel的相关信息可以查看ug1393的Chapter 8。

Vitis的软件加速实现跟Vivado HLS是比较相关的,所以看文档可以发现设计RTL Kernel时寄存器的设计和HLS内的s_axi非常类似。

在该例子中,除了基本的0x00~0x0C寄存器外,只有一个scalar的输入参数。

2.3 Vivado Design Suite — RTL Design

目的:

区别:

无

2.3.1 功能说明

该例子中RTL的功能是实现**B[i] = A[i]+B[i]**硬件加速操作。A和B通过AXI_MASTER接口读出数据,进行计算后再将计算结果写入到B的地址空间内。

该例子中有对应的testbentch,里面使用VIP访问AXI_SLAVE寄存器实现功能仿真。可以自己仿真看下效果。

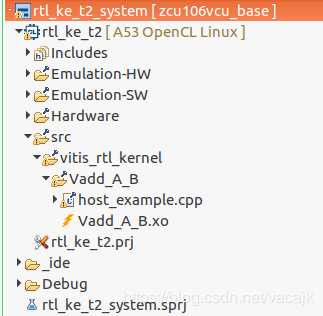

2.3.2 打包xo

步骤2.2中的Vivado RTL Kernel Wizard是通过Vitis打开的,在步骤2.3完成打包后将会自动将Vadd_A_B.xo添加到Vitis工程中去。如下图:

xo是一个压缩文件,解压后可以看到文件目录结构:

.

├── ip_repo

│ └── mycompany_com_kernel_Vadd_A_B_1_0

│ ├── component.xml

│ ├── src

│ │ ├── A_axi_read_master.sv

│ │ ├── B_axi_read_master.sv

│ │ ├── control_Vadd_A_B_vip

│ │ │ └── control_Vadd_A_B_vip.xci

│ │ ├── slv_m00_axi_vip

│ │ │ └── slv_m00_axi_vip.xci

│ │ ├── slv_m01_axi_vip

│ │ │ └── slv_m01_axi_vip.xci

│ │ ├── Vadd_A_B_control_s_axi.v

│ │ ├── Vadd_A_B_example_adder.v

│ │ ├── Vadd_A_B_example_axi_write_master.sv

│ │ ├── Vadd_A_B_example_counter.sv

│ │ ├── Vadd_A_B_example.sv

│ │ ├── Vadd_A_B_example_vadd.sv

│ │ ├── Vadd_A_B_ooc.xdc

│ │ ├── Vadd_A_B_tb.sv

│ │ ├── Vadd_A_B_user.xdc

│ │ ├── Vadd_A_B.v

│ │ └── Vadd_B.sv

│ └── xgui

│ └── Vadd_A_B_v1_0.tcl

├── Vadd_A_B

│ └── kernel.xml

└── xo.xml

可以看出其实就是相当于打包了一个RTL IP,然后加了一个kernel.xml和xo.xml,至于具体的功能我还没研究。

2.4 Using the RTL Kernel in a Vitis IDE Project

目的:

使用GitHub例子中的host.cpp代码替换到自动生成的host_example.cpp中

区别:

GitHub的例子中使用了仿真代码方式,而我这里实际上板进行了实测

2.4.1 代码框架

在该章节中还介绍了host.cpp代码中的实现流程,代码是基于OpenCL的。

最重要的代码如下,用于实际调用RTL相关功能,实现硬件加速。

clEnqueueTask(command_queue, kernel, 0, NULL, NULL);

2.4.2 编译和测试

例子中只进行了仿真,我这里就不需要了

3 编译

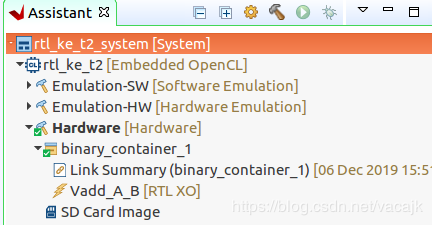

前面提到了我这里使用了硬件实测,如下图:

3.1 注意事项

3.1.1 Compute Units

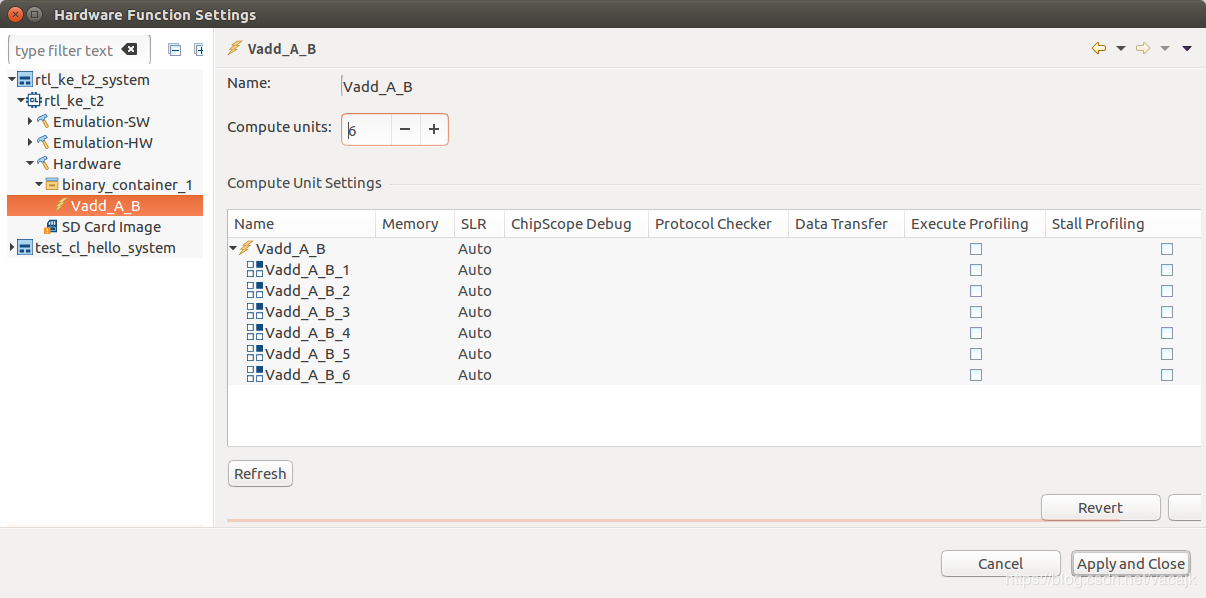

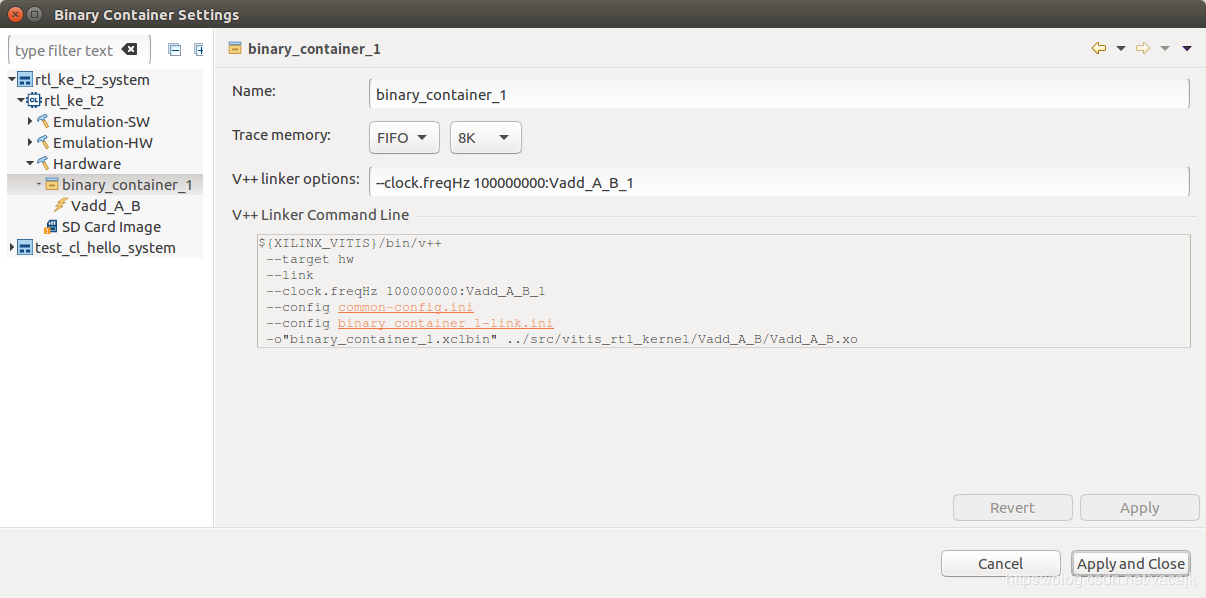

可以看到Vadd_A_B即是我们将要在实现的硬件加速核,他被囊括在binary_container_1中。

在我测试中理解到,Kernel(Vadd_A_B)即是加速实体,要被放到Container(binary_container_1)中。而且可以在配置时实现多组Kernel的例化,这样该就实现了并行加速的功能吧,以后得试试。例化个数的配置如下图:

3.1.2 Kernel Clock Frequency

在文章ZCU106 XRT Vivado工程分析【Xilinx Vitis】中介绍到,Vivado内部的MMCM实现了多个时钟配置,根据Kernel的需要我们可以在Container中进行配置。

需要在V++ linker options中进行配置,如下所示:

--clock.freqHz 100000000:Vadd_A_B_1

3.2 编译

右键点击Hardware,然后选择Build即可开始编译。

编译过程我也没细细研究,可以双击Link Summar查看编译过程。Xilinx的一个新工具Vitis Analyzer可以查看编译中的各种详细的log,简要的log可以在Vitis的Console中查看。

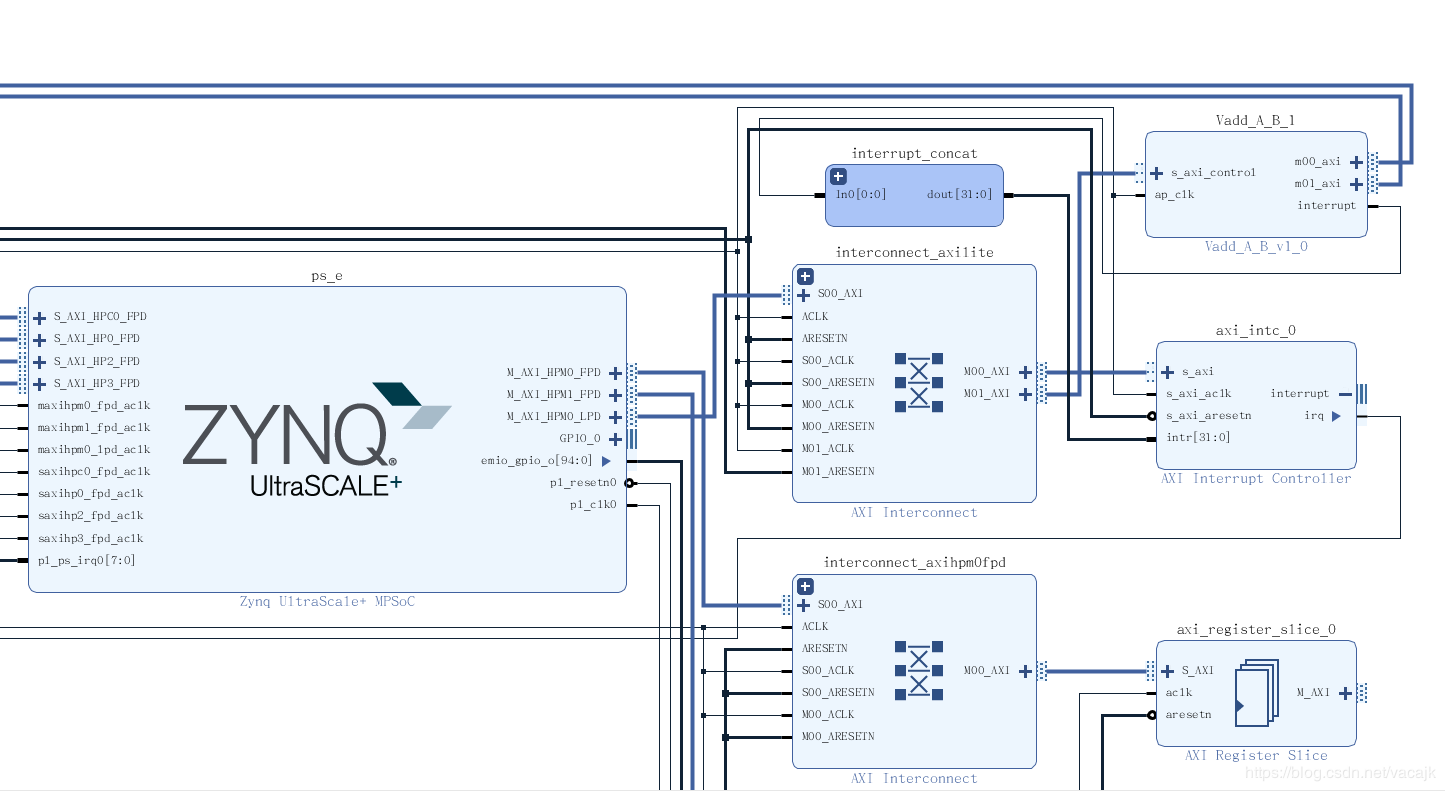

打开Vivado可以查看RTL Kernel Vadd_A_B_1被添加到了工程当中。1个AXI_S,2个AXI_M,1个中断信号连接到了axi_intc_0。并且该IP被连接到了之前按设定的100MHz时钟上。

3.3 SD Card Image

编译完成后Vitis会将将生成的固件放到Hardware/sd_card目录下。

.

├── binary_container_1.xclbin - Vitis生成的包含Kernel的固件

├── BOOT.BIN - Vitis打包好的启动文件

├── image.ub - zcu106vcu_base自带的镜像文件

├── init.sh - zcu106vcu_base自带的脚本

├── platform_desc.txt - zcu106vcu_base自带的描述文件

├── README.txt - Vitis生成的说明文件

└── rtl_ke_t2.exe - Vitis生成的可执行程序

BOOT.BIN 包含了XRT平台的fsbl、u-boot,以及Vitis集成RTL Kernel后生成FPGA bit文件

、

将以上所有文件复制到SD卡,并将MPSOC启动方式切换未SD卡启动即可进行工能测试。

现在有一个疑问就是xclbin中的bit文件和BOOT.bin内的bit文件不知道有什么区别,后面需要研究一下。

4 上板测试

等待板子启动后执行命令进行测试:

root@zcu106vcu_base:~# /mnt/rtl_ke_t2.exe /mnt/binary_container_1.xclbin zcu106vcu_base

[ 60.743975] [drm] Pid 2553 opened device

[ 60.747958] [drm] Pid 2553 closed device

[ 60.752080] [drm] Pid 2553 opened device

INFO: Found 1 platforms

INFO: Selected platform 0 from Xilinx

INFO: Found 1 devices

CL_DEVICE_NAME zcu106vcu_base

Selected zcu106vcu_base as the target device

INFO: loading xclbin /mnt/binary_container_1.xclbin

[ 61.677061] [drm] Finding IP_LAYOUT section header

[ 61.677068] [drm] Section IP_LAYOUT details:

[ 61.681880] [drm] offset = 0x126ad88

[ 61.686148] [drm] size = 0x58

[ 61.689905] [drm] Finding DEBUG_IP_LAYOUT section header

[ 61.693045] [drm] AXLF section DEBUG_IP_LAYOUT header not found

[ 61.698357] [drm] Finding CONNECTIVITY section header

[ 61.704274] [drm] Section CONNECTIVITY details:

[ 61.709318] [drm] offset = 0x126ade0

[ 61.713838] [drm] size = 0x1c

[ 61.717584] [drm] Finding MEM_TOPOLOGY section header

[ 61.720721] [drm] Section MEM_TOPOLOGY details:

[ 61.725766] [drm] offset = 0x126ad58

[ 61.730287] [drm] size = 0x30

[ 61.734998] [drm] No ERT scheduler on MPSoC, using KDS

[ 61.743589] [drm] scheduler config ert(0)

[ 61.743591] [drm] cus(1)

[ 61.747597] [drm] slots(16)

[ 61.750288] [drm] num_cu_masks(1)

[ 61.753255] [drm] cu_shift(16)

[ 61.756744] [drm] cu_base(0x80000000)

INFO: Test completed successfully.

[ 61.759965] [drm] polling(0)

[ 61.778833] [drm] Pid 2553 closed device

root@zcu106vcu_base:~#

root@zcu106vcu_base:~# /mnt/rtl_ke_t2.exe /mnt/binary_container_1.xclbin zcu106vcu_base

[ 88.192855] [drm] Pid 2626 opened device

[ 88.196811] [drm] Pid 2626 closed device

[ 88.200895] [drm] Pid 2626 opened device

INFO: Found 1 platforms

INFO: Selected platform 0 from Xilinx

INFO: Found 1 devices

CL_DEVICE_NAME zcu106vcu_base

Selected zcu106vcu_base as the target device

INFO: loading xclbin /mnt/binary_container_1.xclbin

[ 88.298956] [drm] The XCLBIN already loaded. Don't need to reload.

[ 88.300055] [drm] Reconfiguration not supported

INFO: Test completed successfully.

[ 88.325898] [drm] Pid 2626 closed device

root@zcu106vcu_base:~#

第一次运行时调用了drm的相关驱动,加载了xclbin,然后运行了硬件加速程序,测试通过。

第二次运行时因为已经加载过xclbin,所以直接运行了硬件加速程序,测试通过。

实际的提速效果我这没有测试,但根据经验来说,数据循环次数越多,硬件加速的效果就会越明显,外部调用接口所消耗的时间比重也会越低。

5 总结

使用Vitis和自定义的ZCU106 XRT平台完成了Vitis-Tutorials中的RTL Kernel基本功能测试。

待补充。

————————————————

版权声明:本文为CSDN博主「vacajk」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/vacajk/article/details/103543748