本文转载自:嵌入式领域

赛灵思的文档繁多,本来可以用简单的方法能够实现,却没有简明的文档进行说明,给新进者带来困扰,下面我来介绍下用Vivado工具定义管脚的两种方法。

定义方法一

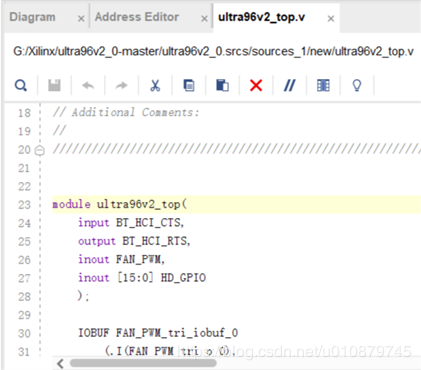

打开顶层设计

上图中input、output、inout四行即为需要定义的芯片与外界通信的管脚。

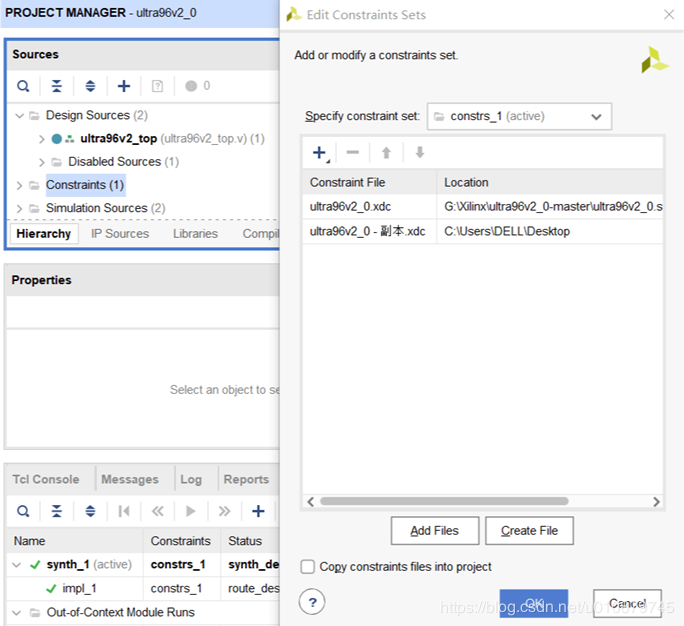

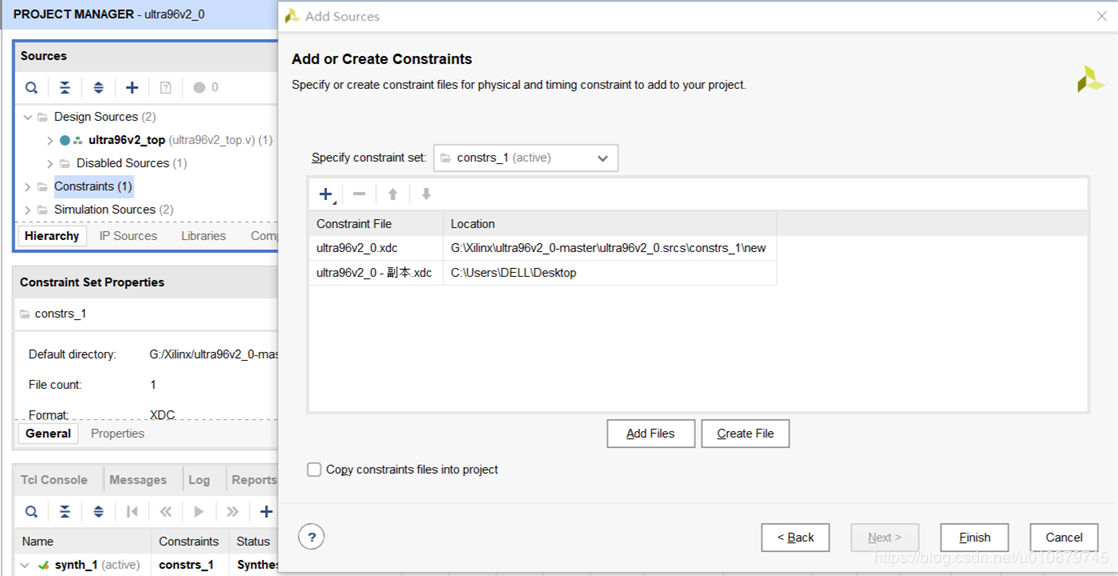

Constraint右键选择以下两种方式之一可加入新的限制文件,实现管脚指定。

上两图副本即为新加入的限制文件。

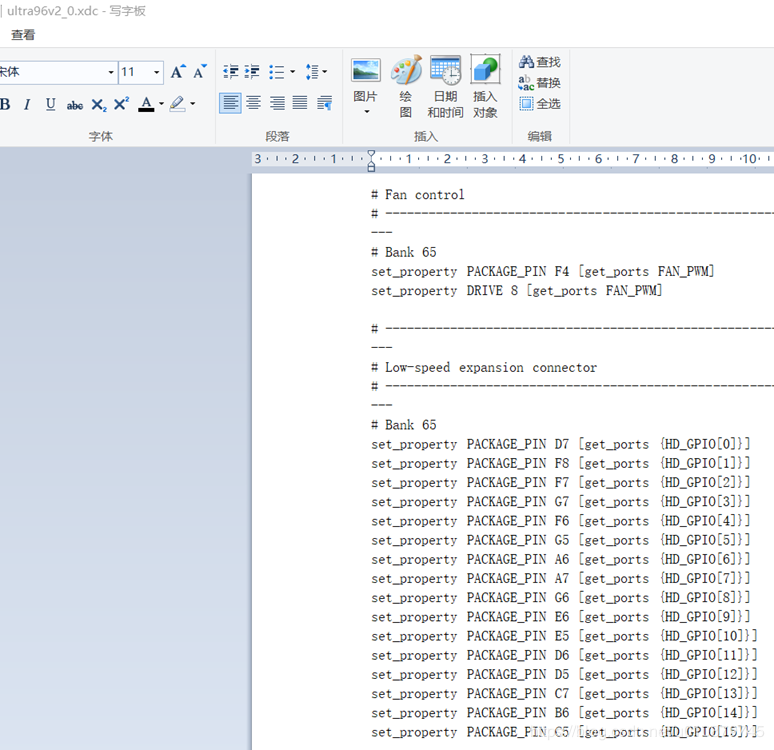

打开限制文件,可看到定义管脚语句。

VivadoXDC约束常用命令 | 电子创新网赛灵思中文社区 http://xilinx.eetrend.com/d6-xilinx/forum/2018-05/12941.html

定义方法二

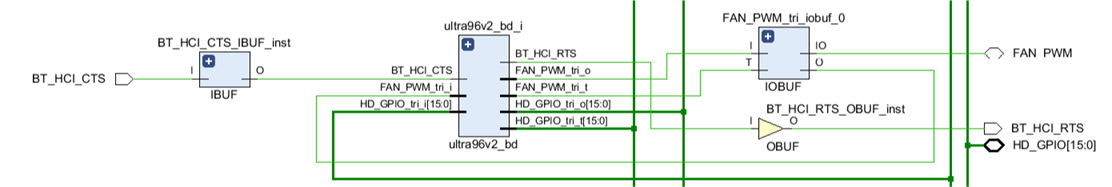

打开右侧原理图

左上角可以看到打开的原理图

局部放大

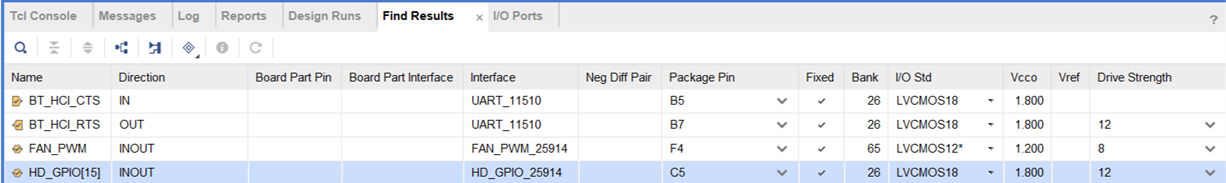

双击I/O Ports选项,编辑管脚

Ultra96的管脚定义分析

打开Ultra96原理图,下图为原理图中无线部分截图,可以看出,BT_HCI_CTS、BT_HCI_RTS是通往无线的串口信号线。

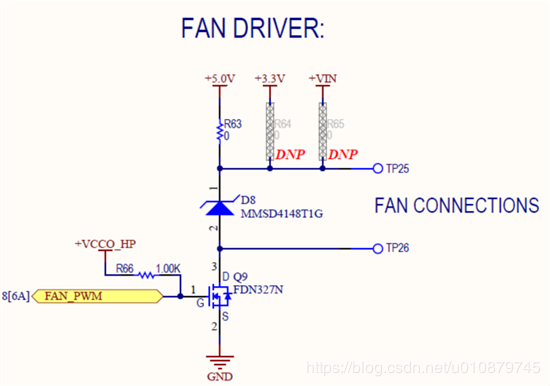

从下图看出,FAN_PWM是风扇控制线。

D_GPIO[0]-[15]为外接低速信号总线。