作者: 碎碎思 OpenFPGA微信公众号

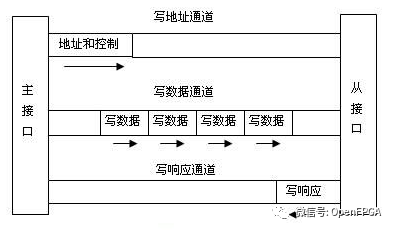

AXI4协议基于猝发式传输机制。在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。主从设备间的数据传输有两种情况,一种是主设备经过写通道向从设备写数据(简称写交易),另一种是主设备经过读通道从从设备那里读取数据(简称读交易)。在写交易过程中,AXI有一个额外的写响应通道,从设备通过该通道向主设备发出信号表示完成写交易。

AXI 协议可以实现:

图4‑13展示了使用读地址和读数据通道如何实现读交易。

图4‑13 读通道结构

图4‑14描述了使用写地址、写数据和写响应通道如何实现一次写交易。

图4‑14 写通道结构

通道定义

五个独立的通道都包含一组标记信息的信号,并且使用双向的 VALID 和READY信号实现握手机制。

当通道上的有效数据或控制信息可用时,发送信息的源设备将使能 VALID 信号。当目的设备接收到数据时,使能READY 信号.当一次交易中最后数据传输完成时,读数据通道和写数据通道都会发出一个LAST 信号。

读地址和写地址通道

读交易和写交易都有各自的地址通道,相应的地址通道承载了一次交易中所有需要的地址和控制信息。AXI 协议支持以下机制:

读数据通道

读数据通道用于传输从设备返回给主设备的数据和读响应信息。读数据通道包含:

写数据通道

写数据通道主要传输从主设备向从设备写数据信息,其包含:

写数据通道的信息总是放入缓存中,当前一个写交易从设备没有做出响应的情况下,以便于主设备进行写交易。

写响应通道

写响应通道是从设备对写交易作出响应的通道。所有写交易使用完成信号。

不是猝发中每个独立数据传输都返回一个完成信号,而是每个猝发完成后一起返回一个完成信号。

寄存器片

每个AXI的通道仅在一个方向上进行信息的传输,各通道之间不需要固定联系。这是很重要的,因为它以添加循环延时为代价, 在任何通道内运行使能一个寄存器片, 这使得在循环延迟和最大工作频率之间的权衡考虑成为可能。

另外,当给定一个互联后,在其内部几乎任何一点处均可以使用寄存器片。它对处理器和高速内存之间实现直接,快速链接非常有利。但使用简单的寄存器片去分离一个较长的路径给低性能外设。

通道之间的关系

地址通道、读数据通道、写数据通道和写响应通道的关系是灵活的。

例如,总线接口上写数据可能比相关写地址早出现。当写地址通道包含寄存器操作多于写地址通道上的操作时,会出现这种情况。也可能是因为写的数据与相关的写的地址出现在同一个周期。

当互联设备必须确定目的地址空间或从设备空间时,互连设备必须重新对齐地址和写数据。确保写数据只对目的从设备有效,是必要的。

两种关系必须满足: