版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/abcdef123456gg/article/details/103187346

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。

容量

BRAM的容量为36Kb,且可当作两个独立的18Kb BRAM使用。对于一个36Kb的BRAM,其最能达到的最大位宽为72bit。

URAM容量为288Kb,一个URAM深度为4K(4×1024),宽度为72bit。

时钟

BRAM 有两个时钟,在 RAMB36E2 的 Primitive 声明中就可以看到这两个时钟 CLKARDCLK 和 CLKBWRCLK 。

URAM 只有一个时钟,在 URAM288 的 Primitive 声明中可以看到该时钟 CLK 。尽管在使用 XPM_MEMORY 实例化 URAM 时可以看到 clka 和 clkb ,但这两个端口最终都连接到 URAM 的物理端口 CLK 上。

初始值

BRAM 的初始值是可以设定的,无论 BRAM 是单端口、简单双端口还是真双端口都可以通过 COE 文件设定其初始值。而 URAM 的初始值只能为0,且无法更改,换言之,其初始值是不可设定的。这也就意味着 BRAM 可以配置成 ROM 而 URAM 不可以。

工作模式

BRAM 可配置为单端口、简单双端口和真双端口,但对于 URAM,不能简单地将这三种模式映射过来,其工作行为如下图所示。可以看到,A/B端口不是独立的,例如,A端口读而B端口写同一地址,读出的是该地址原有数据;A端口写而B端口读同一地址,读出的是新写入的数据。

图片来源:Table 2-6, ug573

实例化方式

对于 BRAM,可采用原语、XPM_MEMORY、RTL代码或者IP Core的方式进行实例化,

但 URAM 目前只支持原语、XPM_MEMORY 和 RTL 代码的方式。相比而言,XPM_MEMORY 的方式更为快捷,也是Xilinx建议的方式。

级联方式

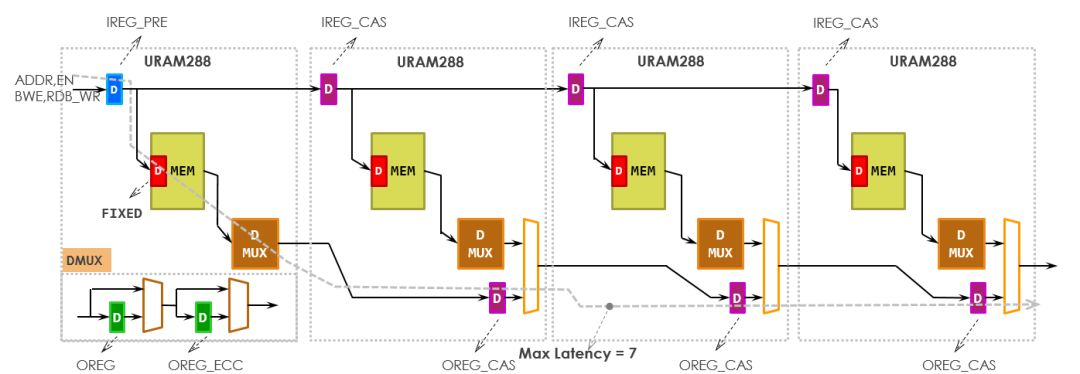

BRAM和URAM都可级联,只是级联方式不同。在使用BRAM时,我们只需要设定宽度和深度,并根据时钟频率合理选择Latency,也就是选择是否需要使用BRAM自带的输出寄存器或Slice中的寄存器。而URAM提供了专门的级联寄存器,同样需要根据时钟频率合理选择Latency,此时会影响到级联寄存器的使用。如下图所示,是4个URAM的级联情形。