FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

注意点

这里博主主要总结两个注意点,也是最常入坑的点:

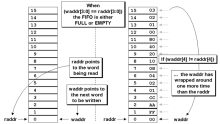

1、异步FIFO的读写计数不准,经常可以碰见FIFO的空标志拉高,但是计数器显示FIFO中还有数据的情况,所以使用FIFO自带的计数器时,一定要小心,只可以使用大概范围,不可以使用精确范围。

2、异步FIFO在复位一段时间后,才可以继续操作,不可以复位后立马把读写使能拉高,因为异步FIFO需要一定的时间进行同步操作。

3、FIFO复位后需要一些时钟之后,才可以进行正常的读写工作。

4、异步FIFO写数据需要经过10个左右的时钟才能从正确读出,这里一定要流出足够的时钟周期,否则会发生错误。

上面的两点一定要注意,否则很容易跳入一个大坑。当然,同步FIFO没有上述的问题。

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/zhangningning1996/article/details/104813549