版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/zhoutaopower/article/details/105257499

1、BRAM 简介

XILINX 系列的 FPGA ,如果想要做一个 RAM,有两种方式:

1、使用逻辑资源组成分布式 RAM,即 Distributed RAM

2、使用 XILINX 专用的 Block RAM,即 BRAM

前者是由 CLB 的 SLICEM 的 LUT 组合而成,构成 RAM 后,可能分布在不同的地方,具有一定的延迟;

后者是 Block RAM 是内嵌专用的 RAM,是 XILINX 做进 FPGA 内的专用资源,具有更好的时序性能;

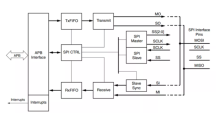

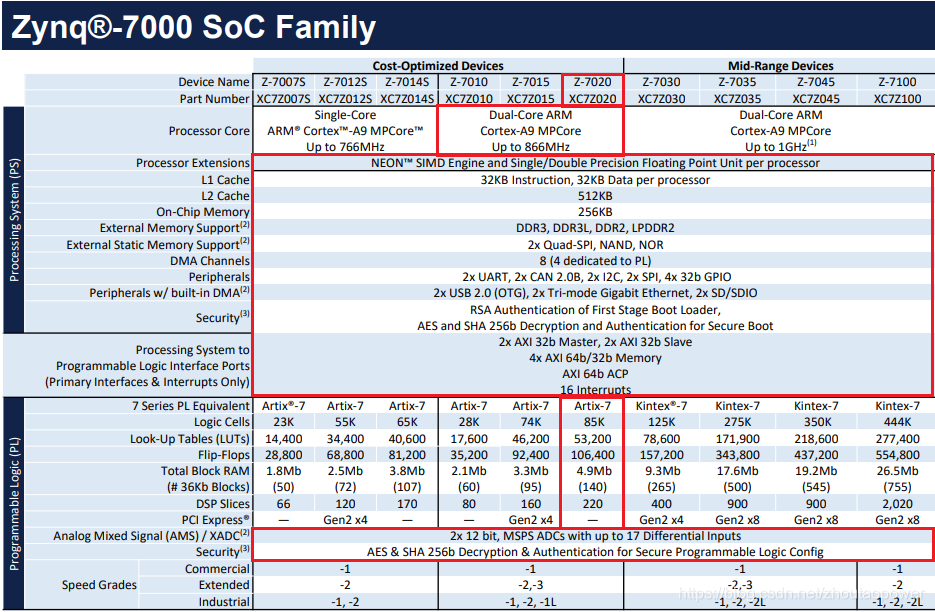

这里我们以 ZYNQ-7000 为例:

可以看到红色方框中,标识出了此款 FPGA 的 BRAM 资源,我们也可以了解到,一个 BRAM 资源大小为 36Kbits(注意,这里是 bits),红色方框的这款含有 140 个这样的 BRAM,也就是一共含有 36Kbits * 140 = 4.9Mbits 大小的 BRAM 资源;

在 XILINX 的官方文档上,介绍这部分的文档是:

pg058-blk-mem-gen.pdf

有兴趣的可以下载来看下;

针对 BRAM 资源的接口形式,主要分为两种:

Native:本地 BRAM AXI4:与 AXI4 总线互联的 BRAM

这里更多的来了解一下 Native 类型的 BRAM,等到要用到 BRAM 挂到 AXI 上的时候,再来仔细分析 AXI Interface 的 BRAM;

较为新的 XILINX 介绍这部分的内容叫 BMG(Block Memory Generator)

2、Block Memory Generator Feature

2.1 Type

按照 BRAM 可以构成的器件类型来分,主要可以分为如下几种:

• Single-port RAM : 单口 RAM • Simple Dual-port RAM:伪双口 RAM • True Dual-port RAM:真双口 RAM • Single-port ROM :单口 ROM • Dual-port ROM:双口 ROM

2.1.0、Signals Descriptions

首先进行信号的描述,常用到信号含义如下表所示:

| Signal Name | Direction | Description |

|---|---|---|

| clka | Input | Port A 的同步时钟信号 |

| addra | Input | Port A 的地址信号 |

| dina | Input | Port A 写操作时候的输入数据信号 |

| douta | Output | Port A 读操作时候的输出数据信号 |

| ena | Input | Port A 的使能信号,在读,写,Rst 的时候需要此信号 |

| wea | Input | Port A 的写使能信号 |

| rsta | Input | Port A 的复位信号 |

| regcea | Input | Port A 的可选后级输出寄存器信号 |

| clkb | Input | Port B 的同步时钟信号 |

| addrb | Input | Port B 的地址信号 |

| dinb | Input | Port B 写操作时候的输入数据信号 |

| doutb | Output | Port B 读操作时候的输出数据信号 |

| enb | Input | Port B 的使能信号,在读,写,Rst 的时候需要此信号 |

| web | Input | Port B 的写使能信号 |

| rstb | Input | Port B 的复位信号 |

| regceb | Input | Port B 的可选后级输出寄存器信号 |

| sbiterr | Output | Single-Bit Error 信号 |

| dbiterr | Output | Double-Bit Error 信号 |

| injectsbiterr | Input | Inject Single-Bit Error: Available only for Zynq-7000 and 7 series ECC configurations. |

| rdaddrecc | Output | Read Address for ECC Error output: Available only for Zynq-7000 and 7 series ECC configurations |

| eccpipece | Input | ECC Pipe Line Register Clock Enable: Available only for UltraScale architecture-based devices. |

| sleep | Input | 动态功耗调整: If sleep pin is High , the Block Memory Generator core is in power saving mode. Available only for UltraScale architecture-based devices |

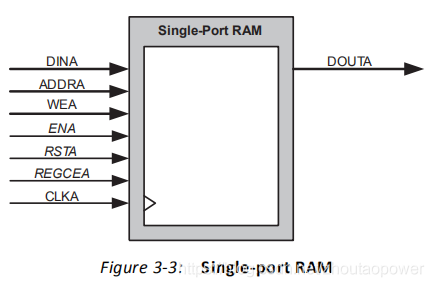

2.1.1、Single-port RAM

XILINX 官方的 pg058 部分描述了 Single-port RAM 的典型应用,可用于处理器暂存数据的 RAM,或者作为查找表等;它的图解如下所示,斜杠的信号为可选信号,其余的是必选信号;

CLKA 为输入的时钟信号,时钟上升沿对数据进行写入/读出

DINA 为写入的数据总线

DOUTA 为读出的数据总线

ADDRA 为地址总线

ENA 为使能端,当 ENA 为 1 的时候,可进行读写操作,ENA 为 0 的时候,无法进行读写

WEA 为写使能,当 ENA 为 1 同时 WEA 为 0 的时候,为读操作;当 ENA 和 WEA 同时为 1 的时候,为写操作;

由于只有一组地址总线,故,单口的 RAM 是无法同时进行读写操作的,只能读、写分开进行;

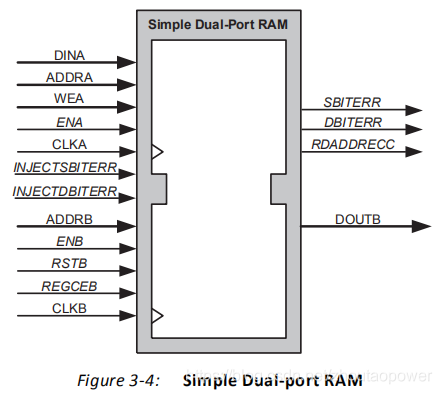

2.1.2、Simple Dual-port RAM

XILINX 官方的 pg058 部分描述了 Simple Dual-port RAM 的典型应用:Content addressable memories, FIFOs

它的图解如下所示:

与单口 RAM 不同的是,伪双口 RAM 输入有两路时钟 : CLKA/CLKB ,独立的两组地址信号 ADDRA/ADDRB,Port A 提供 DINA 写数据总线,作为数据写入的入口;Port B 仅仅提供数据读的功能,读出的数据为 DOUTB;

所以伪双口 RAM 能够提供同时读写 RAM 的功能

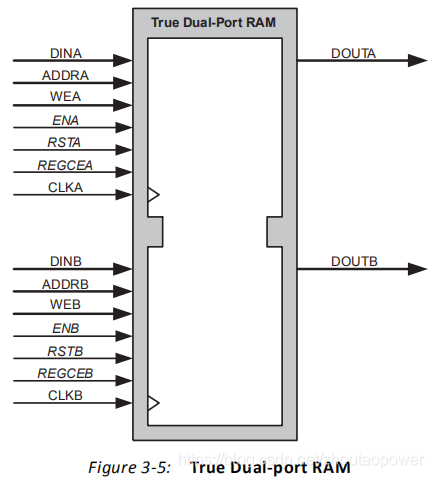

2.1.3、True Dual-port RAM

XILINX 官方的 pg058 部分描述了 True Dual-port RAM 的典型应用:多处理器存储方案,Multi-processor storage

它的图解如下所示:

真双口 RAM 提供了独立的 Port A 和 Port B 的读写功能,既可以同时处在读,也可以同时写,也可以一个读一个写;

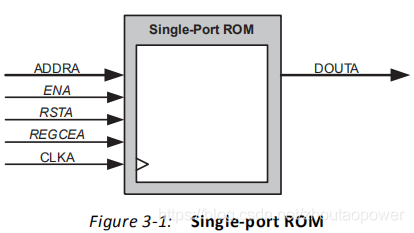

2.1.4、Single-port ROM

BRAM 也可以做成 ROM,典型应用是:Program code storage, initialization ROM,如下图所示

与 Single-port RAM 几乎相同,唯一不同的是,没有 DINA 信号,因为是 ROM,所有不提供写入;

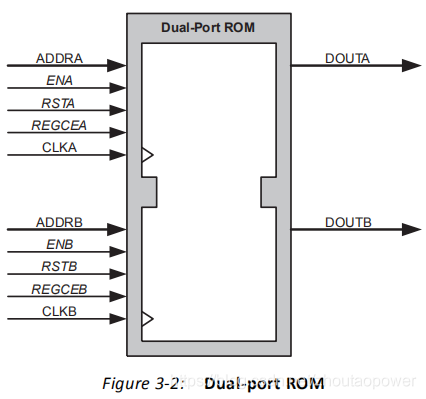

2.1.5、Dual-port ROM

BRAM 也可以做成 ROM,典型应用是:Single ROM shared between two processors/systems

双口的 ROM,提供 Port A 和 Port B 两路读;

2.2、Selectable Memory Algorithm

使用 XILINX 的 BMG 生成上述类型的 RAM/ROM 的时候,有一个可选项叫做生成的算法,这里有三种可选的算法:

Minimum Area Algorithm : 面积最优 Low Power Algorithm:功耗最低 Fixed Primitive Algorithm:固定原语

2.3、Configurable Width and Depth

在使用 BMG 生成 RAM 的时候,位宽支持配置从 1 bits ~ 4608 bits,深度支持大于等于 2,具体最大能够配置出多少 RAM,需要查看当前的器件手册中包含的 BRAM 的个数;

2.4、Selectable Operating Mode per Port

BRAM 组成 RAM 后的读写模式可以分为三种,并且 Port A 和 Port B 可以独立配置:

1. Write First Mode

2. Read First Mode

3. No Change Mode

这些 mode 是针对一个 Port 来说的;

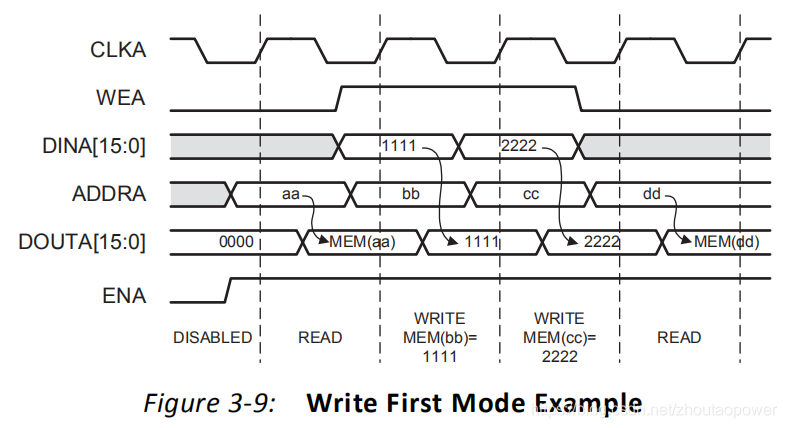

2.4.1、Write First Mode

这种模式下,写操作的优先级高于读操作,它的时序如下所示:

这个时序很生动的描述了这种 mode :

1、刚刚开始,ENA 信号一直为 0,即,没有使能;

2、第一个虚线,也就是 CLKA 的上升沿位置,采到 ENA 为 1,同时 WEA 为 0,则代表为 READ 时序,同时,在这个上升沿,采集到 ADDRA 上为 aa(ADDRA 为并行地址总线),那么就会在获取到 aa 这个地址中的值后(经过了一点延时),将数据打到 DOUTA[15:0] 上,所以这里可以看到 DOUTA 上是 MEM(aa),也就是 aa 这个 RAM 地址中存储的数据;

3、第二个虚线,CLKA 上升沿的时候,同样会检测 ENA 和 WEA,此刻,它们都为 1,则代表 WRITE 时序来了,此刻采集到写入数据总线 DINA 上的数据为 1111,地址总线上是 bb,那么此刻是将地址 bb 的值放到 DOUTA 上呢,还是直接将 DINA 的值放到 DOUTA 上呢,这个 Operating Mode 就是解决这个问题的,在 Write First Mode 的情况下,DINA 的 1111 数据直接被送到了 DOUTA 总线上,同时,MEM(bb) 的内容被写入 1111,;

4、第三个虚线,CLKA 上升沿的时候,同理,2222 数据被直接写到 MEM(cc),同时被输出到 DOUTA 上

5、第四个虚线,CLKA 上升沿的时候,WEA 信号被拉到 0,但是 ENA 信号还是 1,说明当前不存在 WRITE了,只有 READ 时序,那么会将 ADDRA 上采集到的 dd 地址的数据读出到 DOUTA 上;

2.4.2、Read First Mode

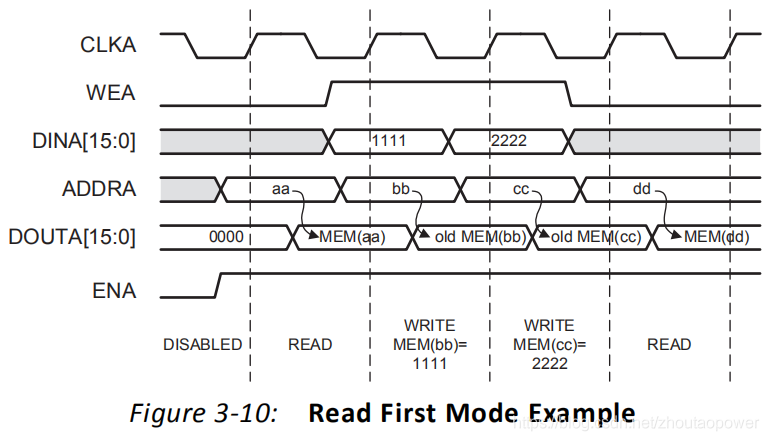

这种模式下,读操作的优先级高于写操作,它的时序如下所示:

有了 Write First Mode 的分析过程,分析这个也不算困难:

1、刚刚开始,ENA 信号一直为 0,即,没有使能;

2、第一个虚线,也就是 CLKA 的上升沿位置,采到 ENA 为 1,同时 WEA 为 0,则代表为 READ 时序,同时,在这个上升沿,采集到 ADDRA 上为 aa(ADDRA 为并行地址总线),那么就会在获取到 aa 这个地址中的值后(经过了一点延时),将数据打到 DOUTA[15:0] 上,所以这里可以看到 DOUTA 上是 MEM(aa),也就是 aa 这个 RAM 地址中存储的数据;

3、第二个虚线,CLKA 上升沿的时候,同样会检测 ENA 和 WEA,此刻,它们都为 1,则代表 WRITE 时序来了,此刻采集到写入数据总线 DINA 上的数据为 1111,地址总线上是 bb,由于是在 Read First Mode 的情况下,DOUTA 读出的数据是 bb 地址的数据,读操作完成后同时,MEM(bb) 的内容更新为 1111,;

4、第三个虚线,CLKA 上升沿的时候,DOUTA 读出的数据是 cc 地址的数据,读操作完成后同时,MEM(cc) 的内容更新为 2222;

5、第四个虚线,CLKA 上升沿的时候,WEA 信号被拉到 0,但是 ENA 信号还是 1,说明当前不存在 WRITE了,只有 READ 时序,那么会将 ADDRA 上采集到的 dd 地址的数据读出到 DOUTA 上;

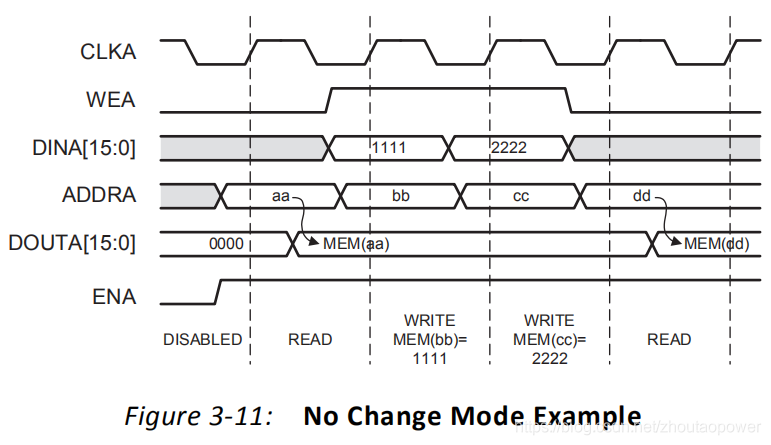

2.4.3、No Change Mode

还有一个 No Change Mode,这个 No Change 指的是当在写的时候, DOUTA 读的数据总线数据保持不变,也就是 No Change;

可以看到,当在往 RAM 里面写的时候,DOUTA 读出的数据保持了不变,即,一直为 aa 的内容,直到 WEA 被拉低,重新进入 READ 模式;

综上所述,这几种模式,主要都是针对的是读数据总线的行为,是直接读出 DINA 呢?还是读出旧的内存地址的数据呢?还是在写的时候被拉住;

2.5、Selectable Port Aspect Ratios

支持 Port A 和 Port B 配置不同的位宽,甚至同一个 Port 配置 Read 和 Write 的位宽不同;

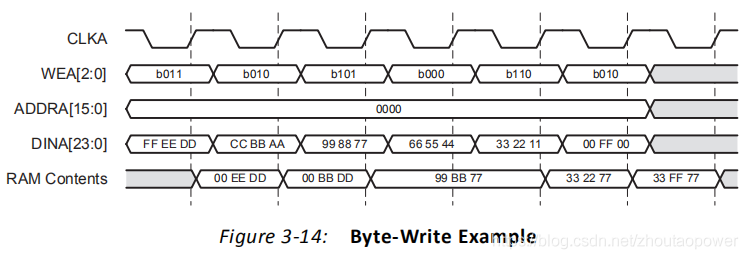

2.6、Optional Byte-Write Enable

BMG 支持可选的一个叫做 Byte-Write 模式,这是一个针对 Write 的模式,在这个模式下,WEA 信号由之前的 1 bit 扩展为了 N 个 bit,在这 N 个 bit 中,1 代表对应的 DINA 中对应 Bytes 会被更新到 ADDRA 对应的地址上去,如果 N bit 中,0 代表对应的 DINA 对应的 Byte 不会被更新到 ADDRA 对应的地址上去,有点拗口,下面是一个基于 Singal-port RAM,输入数据总线 DINA 为 24 bits 宽度,也就是 3 个 Bytes,WEA 为 3 个 bit 宽度,直接看 Timing

DINA 的每个 Byte,对应到 WEA 的每一个 bit,可以看到:

1、第一个虚线 CLKA 上升沿,WEA[2:0] 是 3b'011,ADDRA 是 0x0000 地址,DINA[23:0] 是 FF EE DD,那么他的行为是,由于 WEA=011,代表控制器会去将 DINA 的 后面两个 Bytes 更新到 RAM ADDRA 对应的地址上去,也就是 EE DD 被更新到 0000 的对应位置;

2、第二个虚线 CLKA 上升沿,WEA[2:0] 是 3b'010,ADDRA 还是 0x0000 地址,DINA[23:0] 是 CC BB AA,那么它的含义是,将 BB 更新进去,也就是看到 RAM Contents 内容为 00 BB DD

3、第三个虚线 CLKA 上升沿,WEA[2:0] 是 3b'101,ADDRA 还是 0x0000 地址,DINA[23:0] 是 99 88 77,那么它的含义是,将 99 和 77 按照位置定义关系更新进去,也就是看到 RAM Contents 内容为 99 BB 77

4、第四个虚线 CLKA 上升沿,WEA[2:0] 是 3b'000,所以即便是 DINA 有数据,那么 RAM 内容也不会被更新进去;

5、第五个虚线 CLKA 上升沿,WEA[2:0] 是 3b'110,ADDRA 还是 0x0000 地址,DINA[23:0] 是 33 22 11,那么它的含义是,将 33 和 22 按照位置定义关系更新进去,也就是看到 RAM Contents 内容为 33 22 77

6、第六个虚线 CLKA 上升沿,WEA[2:0] 是 3b'010,ADDRA 还是 0x0000 地址,DINA[23:0] 是 00 FF 00,那么它的含义是,将 FF 按照位置定义关系更新进去,也就是看到 RAM Contents 内容为 33 FF 77

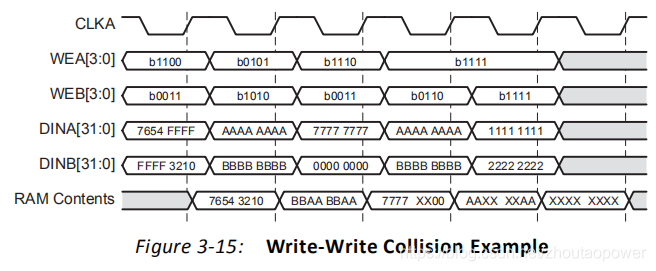

2.7、Collisions

既然是支持多 Port 同时写入,那么就会存在这个冲突的问题,在冲突发生的时候,存储内容不可预知;

冲突主要出现在一下场景:

2.7.1、Write-Write Collision

以 Byte-Writes 为例,假设 Port A 和 Port B 的 ADDR 都是 0x0000;

如上图所示:

1、第一个虚线时钟上升沿,WEA 是 1100,WEB 是 0011,所以写入的内容正好错开,并不冲突

2、第二个虚线时钟上升沿,WEA 是 0101,WEB 是 1010,所以写入的内容正好错开,也不冲突

3、第三个虚线时钟上升沿,WEA 是 1110,WEB 是 0011,第三个 bit 冲突,往同一个地址写内容,所以看到的是 7777 XX00,其中的 XX 是不可预知的内容;

后面的分析类似,不在赘述;

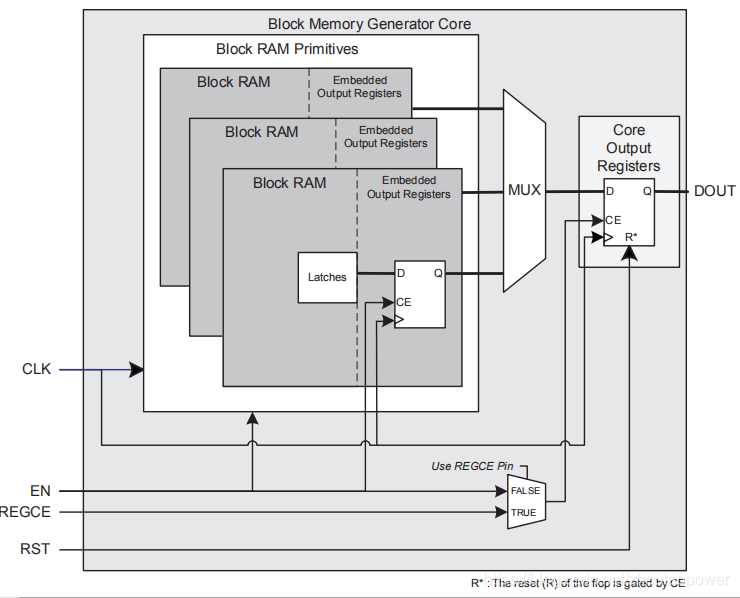

2.7、Optional Output Registers

BMG 允许可选的在输出级增加一级寄存器,来改善输出性能;

可以选择在两个输出的地方增加寄存器:

1、在每个 Block RAM 输出的地方增加寄存器;

2、在整个 BMG Core 输出的地方增加寄存器;

这两个配置都可以针对 Port A 和 Port B 进行单独的配置;

Notes:增加一级输出寄存器,会增加一个 Clock Cycle 的延时;

如果是使用每个 Block RAM 输出端增加 Register,这个触发器是属于 BRAM 的内部资源,不会占用其他的 FPGA 资源;如下图所示:

Block RAM 中的那个寄存器就是指的第一种在输出端增加寄存器;

Core Output Register 那个寄存器,就是第二种,在整个 BMG 输出端增加 Register 的方式;