本文转载自:ZYNQ微信公众号

前言:

都知道FPGA的启动方式有很多种,比如JTAG、SPI,BPI,SeletMAP,Serial等等吧,又分为主从即Master和Slave(时钟由FPGA的管脚发出,专用的CCLK信号为主,否则为从,有的配置有辅助时钟EMCCLK,它由外部的晶振提供,从FPGA的EMCCLK输入,经过专用的逻辑,再从CCLK管脚输出给想用的器件,),那么问题来了,配置失败怎么办呢??????????????看DONE管脚呀,你已经失败了 ,一般情况下DONE管脚是低电平,另寻途径了 只有。。。。。。

只有。。。。

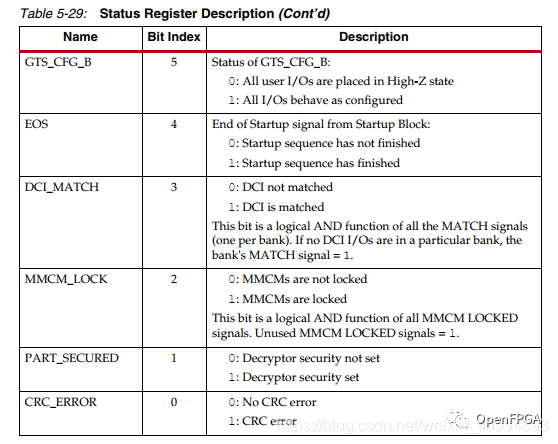

只有一个办法,厂家已经给你想好了 看状态寄存器(相应手册的),它可以很快的辅助你找到配置失败的原因,不管你是哪个系列的或者使用的是ISE也好,Vivado也罢,Xilinx FPGA的状态字,在它的所有系列器件当中,关于状态位的定义基本保持一直,但是也有一些细微的差别,建议看相应系列的数据手册,比如我所要调试的时V-7,我查看Ug470

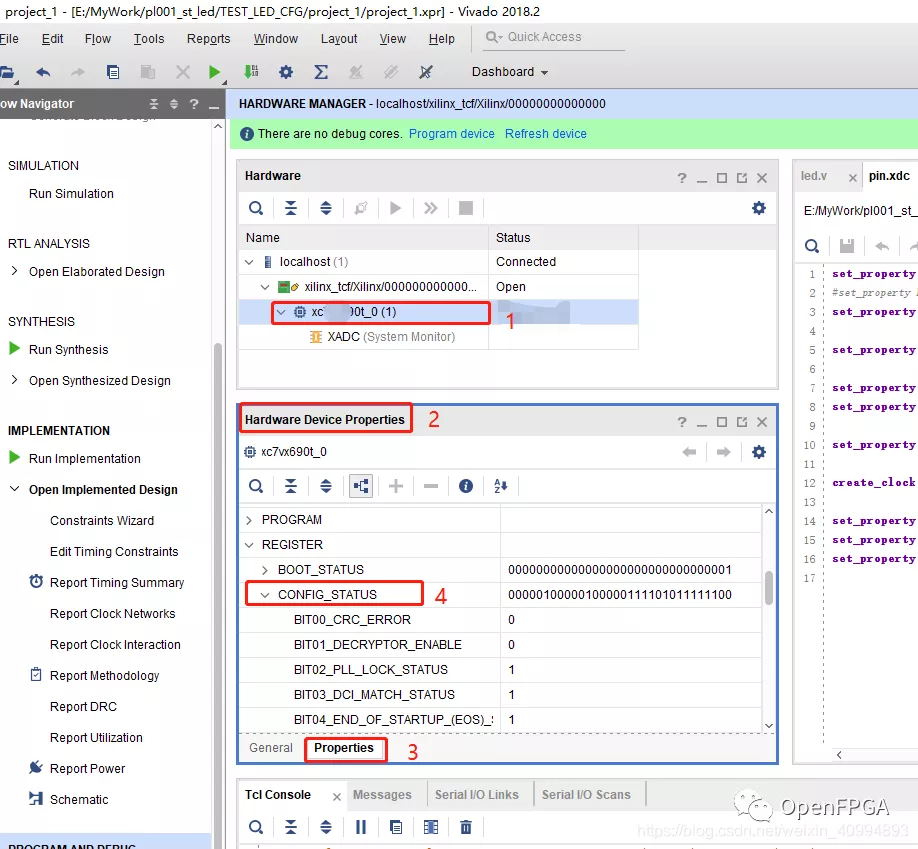

每一位的解释已经很清楚了 ,那么我们怎么读出这些状态字呢,首先我们拿出一块FPGA,连接好下载线和板子,板子上电,打开JTAG,Hardware Manager 窗口显示如下:

将鼠标选中1(我们的器件),擦看2处,点击3处,查看4处,我们来展开配置状态的寄存器,同时对照上面的对每一位的解释大概说一下把,

只有BIT02 PLL_LOCK, BIT03 DCI_MATCH, BIT11 INIT_B_INTERNAL, BIT12 INIT_B_PIN(即初始化状态和时钟及DCI部分)的值必须是1;

BIT08-10 MODE PINS(配置模式),BIT21 SECURITY_STATUS, BIT25-26 BUS_WIDTH,BIT28 PUDC_B根据FPGA和板子具体的设定,可以为1或者0,其他都必须是0。

这样大概就能够判断你的板子的状态了,如果出现其他的值,那么可以能你的配置电路出现了问题,还有其他的出现的比较典型的值,下次再给大家讨论吧。