版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/zhangningning1996/article/details/105308963

基于FPGA的FIR滤波器滤波

项目简述

FIR IP的定制及讲解

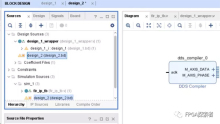

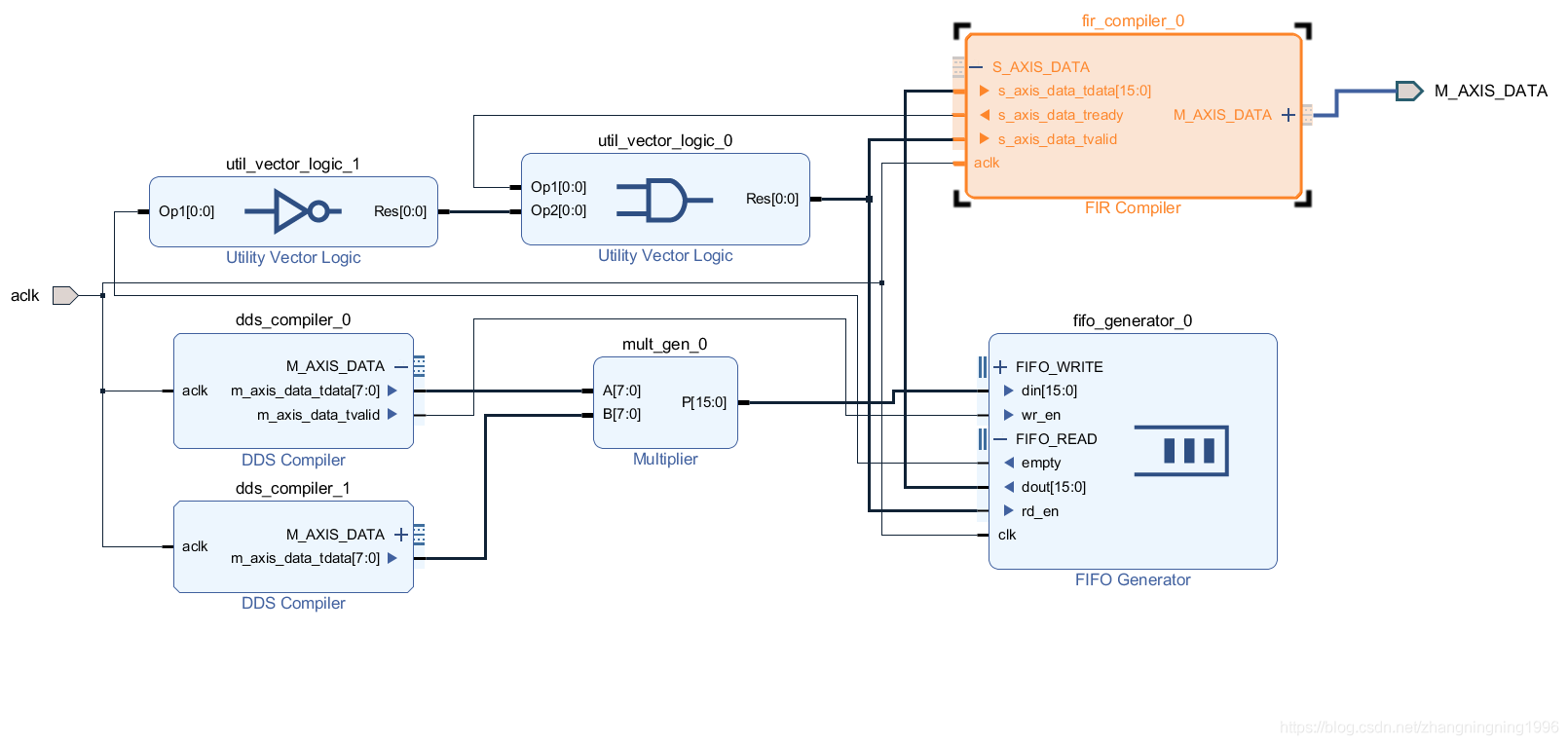

Block Design的设计

测试模块的代码

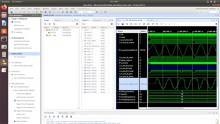

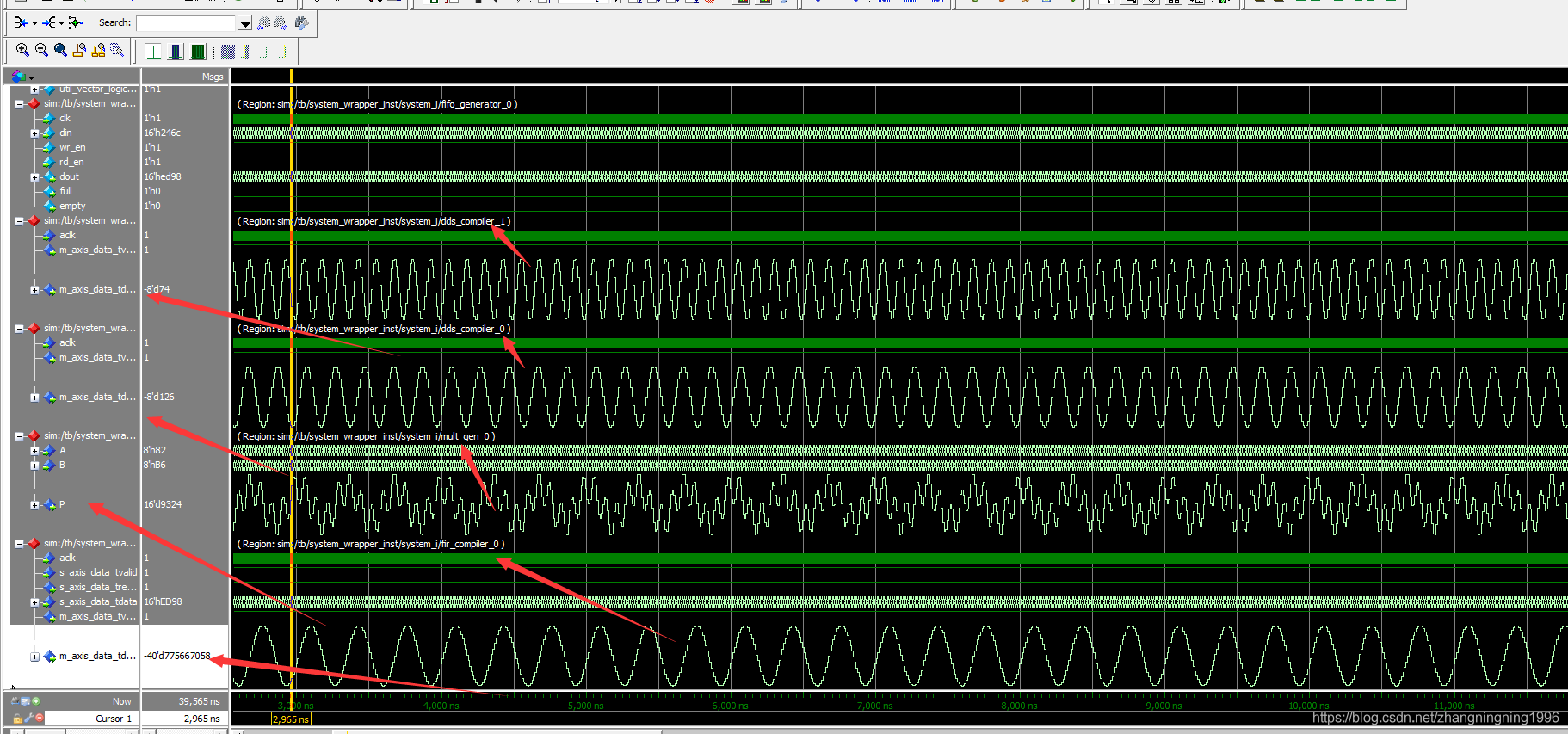

仿真测试结果

总结

项目简述

上一篇论文中,我们已经讲解了DDS的IP与混频的实现。本篇论文我们将接着上篇文章接着做,在混频之后的信号进行滤波处理。数字滤波器主要有FIR、IIR两种滤波器,但在FPGA中几乎看不到使用IIR滤波器,因为IIR滤波器存在的有限字长效应经反馈后会使得系统不稳定。当然IIR滤波器也有优点,相比同样的频率响应,IIR滤波器的阶数要远小于FIR滤波器。其中因为FIR滤波器的稳定性得到了广泛使用,所以我们主要讲解FIR滤波器。在后面的文章中,我们会手写滤波器代码,并且学习现在信号处理中最重要的内容——自适应信号处理。我们按照循序渐进的步骤,先讲解FIR滤波器IP的使用。

FIR IP的定制及讲解

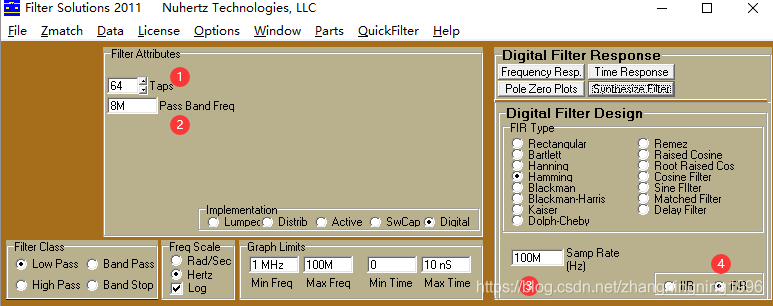

我们定制FIR滤波器的IP核,必须知道响应的FIR系数的相关信息。这里给同学们提供两种方法:一是使用MATLAB,MATLAB中由专门的库供我们设计‘满足我们要求的函数;二是使用小软件Filter Solutions(随工程一起放入群中,需要的进群自取),使用该工具可以更加方便的设计出来滤波器。由于第二种简单,我们这里以第二种为例。

我们上一篇文章的混频是8MHz与5MHz的相乘,所以我们这篇文章的目的是设计一个低通滤波器滤除13MHz的成分。FIR的设计方法在数字信号处理中有两种方法,最常用的就是窗函数法。这里我们将使用汉明窗进行进一步的设计。整个小软件进行如下的配置:

1、设计滤波器的阶数,我们这里选择了64阶

2、设置低通滤波器的通带频率是8MHz

3、设置采样频率是100MHz

4、使用FIR滤波器

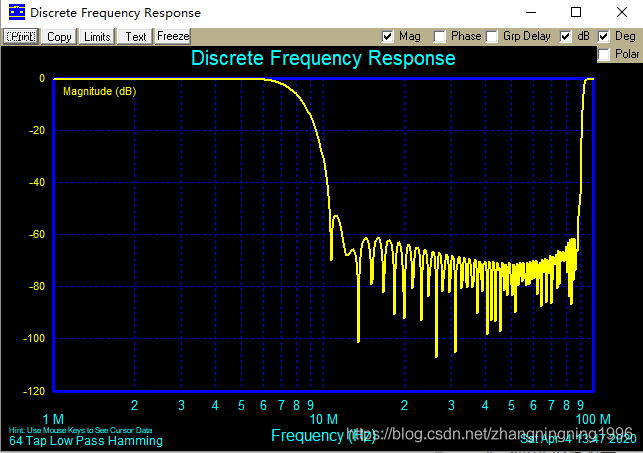

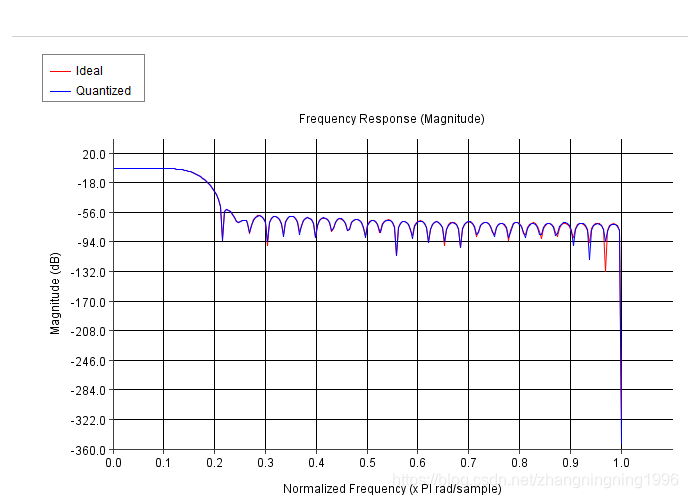

5、点击Frequency Resp观察幅频与相频响应,如下图:

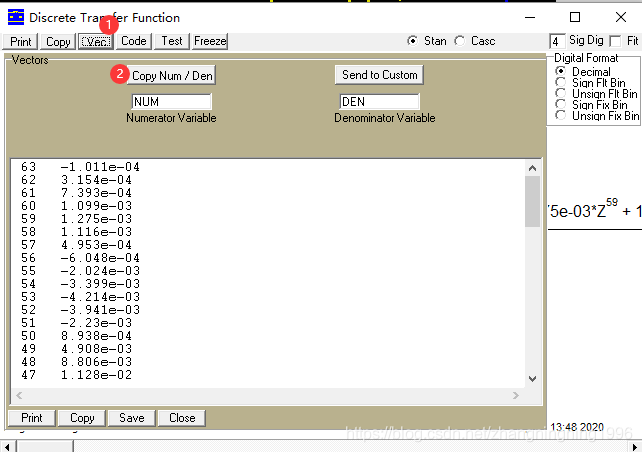

点击Synthesize Filter,再点击其中的vec,如下图:

点击Copy Num/Den复制出相应的系数填入FIR IP的定制界面。

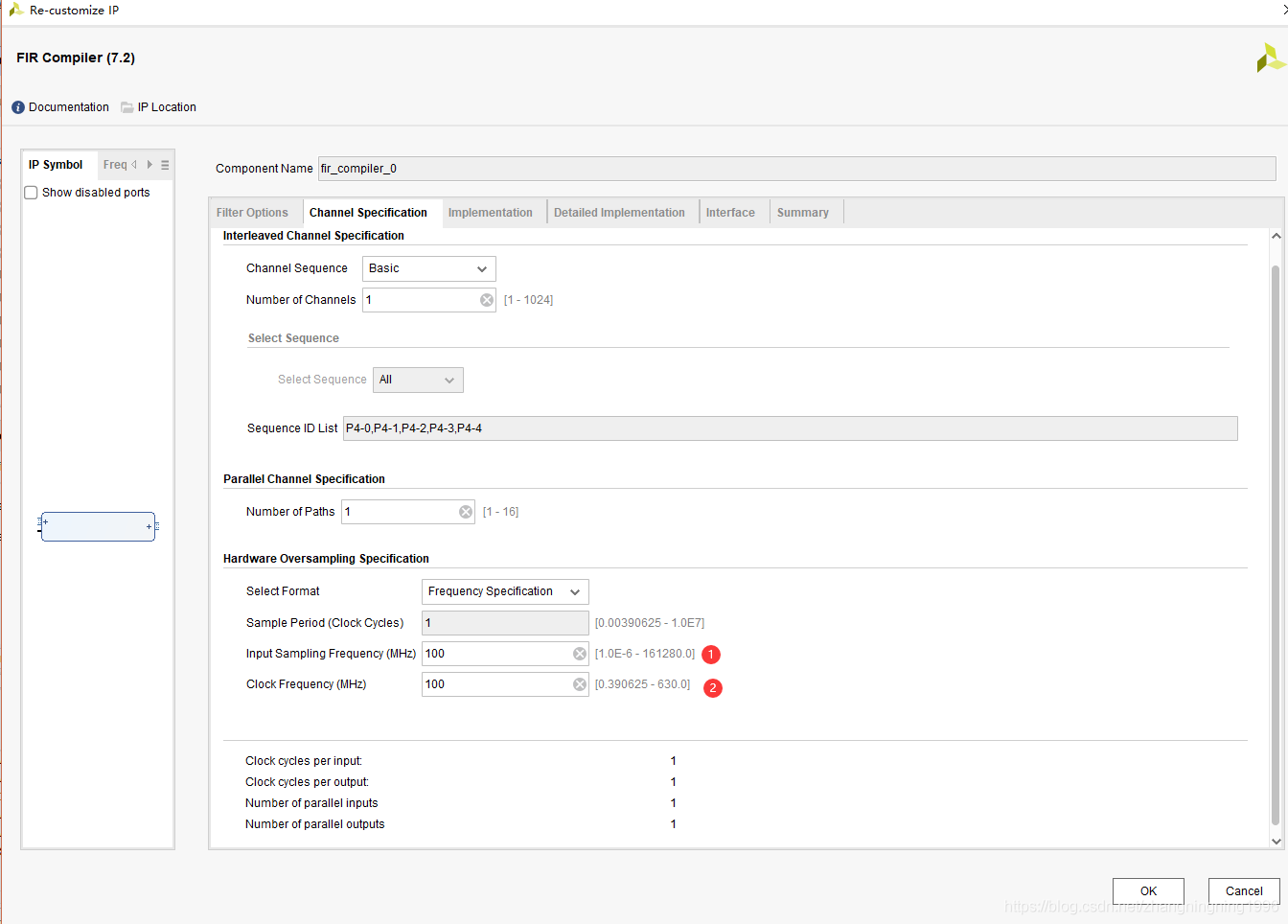

进入Xilinx的FIR IP订制界面,我们可以发现上述界面,其中对我们需要特别关注的配置具体说明一下:

1、我们这里选择系数向量,是指我们直接再IP的定制界面输入相应的滤波器系数。

2、我们将滤波器的系数输入到2中,注意这里可以是小数。

3、这里我们选择典型的单倍速率滤波器就可以。

这里我们选择FIR滤波器的抽样频率与参考频率都是100MHz,也就是说整个滤波器是全流水线结构。

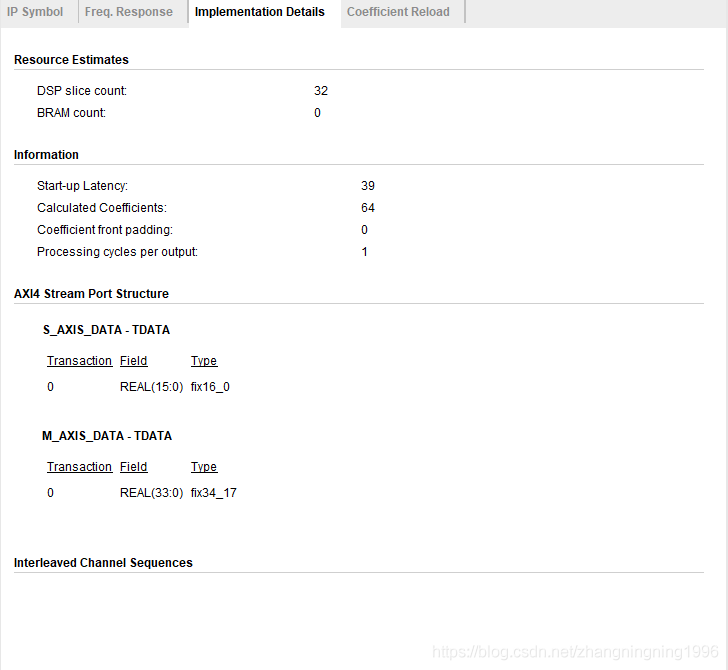

1、这里选择滤波器系数整数部分的量化位宽。

2、在这里输入滤波器系数小数部分量化的位宽

3、这里对我们输入数据进行描述,我们这里使用有符号数、整数、位宽为16位、全精度类型,设置如3,4,5所示。

IP定制界面其余选择默认即可,想具体了解其中配置所代表的意义,可以查阅一下技术手册。

配置完成之后,我们查看一下滤波器的幅频响应与输入输出数据的位数关系,如下:

Block Design的设计

我们紧接着上一章我们设计的混频的工程继续设计该项目的block design,如下图:

上面便是这次实验的block design,我们除了测试模块没有写一句代码。上面的功能主要是把5MHz与8MHz的正弦波进行混频,然后再进行低通滤波,将其中3MHz分量的正弦波滤除出来。

测试模块的代码

我们为了验证我们工程的正确性,对我们搭建的block design进行书写测试模块的代码,如下:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : tb.v

// Create Time : 2020-04-04 15:35:56

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module tb;

wire [15:0] P ;

reg aclk ;

wire [39:0] M_AXIS_DATA_tdata ;

wire M_AXIS_DATA_tvalid ;

initial begin

aclk = 1'b0;

end

always #5 aclk = ~aclk;

system_wrapper system_wrapper_inst(

.M_AXIS_DATA_tdata (M_AXIS_DATA_tdata ),

.M_AXIS_DATA_tvalid (M_AXIS_DATA_tvalid ),

.aclk (aclk )

);

endmodule

仿真测试结果

我们将上面的实验进行Modelsim仿真,仿真的测试结果如下:

从上面的图形中可以看出,我们从上面的波形可以看出来我们成功将13MHz的正弦波滤除掉,只剩下3MHz的正弦波分量。