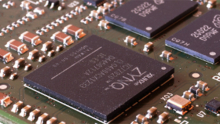

作者:VagueCheung

在使用ZYNQ进行开发设计时,往往需要对一些GPIO引脚进行配置,传统的配置方法通常在PL端进行管脚约束之后在Verilog代码中对相应引脚进行配置。这样如果开发过程中一旦有需要对管脚配置进行修改的话,那么就必须重新进行综合、布局布线、生成比特流文件,如果设计工程相对复杂的话,完成整个过程通常需要相当长一段时间。影响开发效率。

此时,如果将配置引脚的逻辑放在PS端进行的话,更改配置的话就无需对整个工程在进行综合、布局布线、生成比特流文件。只需在SDK中直接修改即可,下面介绍如何将想要配置的GPIO管脚扩展到PS端。(傻瓜式按图一步接一步)

1、双击打开ZYNQ IP,选择Peripheral I/O Pins勾选GPIO EMIO。

2、选择MIO Configuration,打开I/O Periphrials下拉菜单,勾选EMIO GPIO,扩展宽度可以选择1~64,这里我选择4意思就是可以扩展4个GPIO。

3、配置完后,ZYNQ IP会出现增加的GPIO扩展接口,接口名称自己设定。

4、接下来在PL端的XDC约束文件中对需要配置的GPIO引脚进行物理约束。

5、执行一次综合、布局布线、生成比特流文件,打开SDK程序,在程序中对扩展的GPIO进行配置。配置代码如下:

注意:PS端扩展的GPIO序号应从54开始118结束,因为在ZYNQ出厂PS端的前53个引脚已经被其他接口使用。PS端的54则对应PL端约束的[0],其他同理一一对应。

这样一来如果需要修改GPIO配置信息只需修改SDK代码即可,方便快捷提高开发效率。

原文链接:https://www.cnblogs.com/VagueCheung/p/15010479.html?utm_source=tuicool&u...