本文转载自:FPGA大叔的博客

对FPGA而言,时钟就是脉搏,必须理解透彻!

一、如何知道器件所支持的时钟频率?

举例说明:

DDR3 型号: MT41J256M16xx-125

(记住这个常用型号,后文还是以此型号讲解)

FPGA 型号: XC7K325TFFG900-2 (常用FPGA型号)

datasheet : MT41J512M8RH-125:E(DDR3)、DS182(FPGA)

1.1DDR3芯片的带宽、位宽和最大IO时钟频率

翻看DDR3对应型号MT41J256M16XX-125的数据手册,可以看到:

图1. DDR3 Part Numbers

IO时钟频率:

根据Part Number 中的“-125”我们就可以找到图中的tCK = 1.25ns,就可以算出芯片支持的最大IO时钟频率:1/1.25ns = 800Mhz;此处的IO时钟频率也就是DDR3的频率;

位宽:

根据Part Number 中的“256M16”我们可以找到图中2所指出的地方,这里的16是代表芯片的数据位宽是16位(也就是16根数据线)。

注意:

1. 当一个FPGA上挂多个DDR,如4片ddr3,位宽则会相应增大;16*4 = 64bit,再乘以DDR3的突发长度BL=8;那么程序设计里DDR3的读写位宽就变成了16*4*8=512bit; (这里留个印象,再后文IP例化及程序设计部分还会讲到,到时候对应起来看更容易理解)

2. 明明是512M的DDR,为什么又写成256M呢?因为256M16是16根数据线16bit,对应过来就是2个byte;256M *16bit = 512MByte; 一般大B 指的是Byte,小b指的是bit;

带宽:

由于是DDR方式传输数据(上升和下降沿都传输),所以芯片的一根数据线上的传输速率 = 2*800Mhz = 1600MT/s。其实就是1600Mbit/s;

带宽就是16根数据线同时传输的数据速率 = 1600Mbit/s x 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s

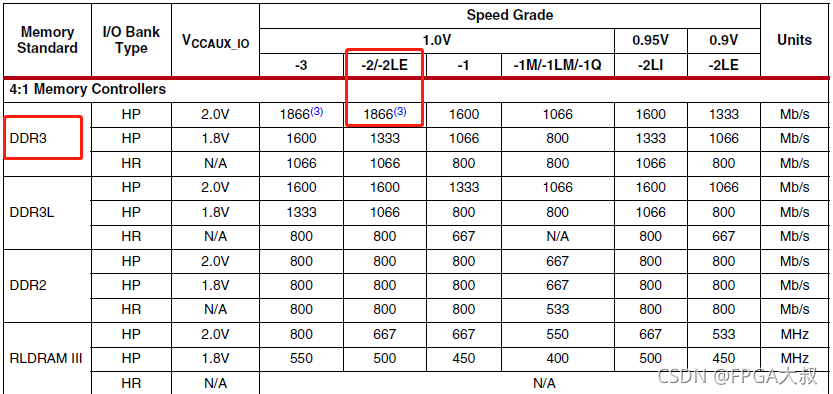

1.3FPGA所支持的最大频率

翻看k7数据手册ds182可以看到:

图2. k7系列支持的DDR速率

k7系列的FPGA所支持的DDR3传输速率高达1866MT/s,这里需要跟硬件工程师具体了解了解,实际使用最高还是1600MT/s,对应频率= 1600M/2= 800Mhz;

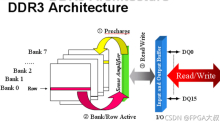

二、时钟结构

图3. 时钟结构

从图中,我们可以看到,主要有两个时钟:

①参考时钟 : 必须为200Mhz

②系统时钟 : 系统输入时钟

那么对应到MIG IP核又是如何定义的呢?继续往下走

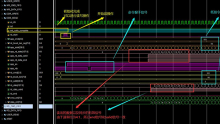

三、MIG IP核的时钟:

3.1clock period时钟

图4. Clock Period

这里①Clock Period设置的参数就是 MIG 的PHY 接口对DDR3的时钟,也就是DDR3芯片实际跑的IO时钟频率,它由system clock(主时钟)倍频而来,最大频率不能超过DDR3 和MIG支持的最大频率中的最小值(前文已讲解如何查看器件所支持的最大频率)。

对应到MIG 例化的信号:

.ddr3_ck_p (ddr3_ck_p ), //连接DDR管脚 .ddr3_ck_n (ddr3_ck_n ),

3.2 ui_clk

图4下面②有个4:1,说明MIG 输出到app接口上的时钟ui_clk = 800M/4=200M ,即到时我们在写RTL逻辑代码时操作MIG核时,用的就是这个200M时钟;

注:当我们选择800M时钟时,下面的PHY to Controller Clock Ratio 只能选择4:1;对应过来ui_clk最大为200M;当我们clock period时钟选择小于800M时,这里可以选择4:1 / 2:1;

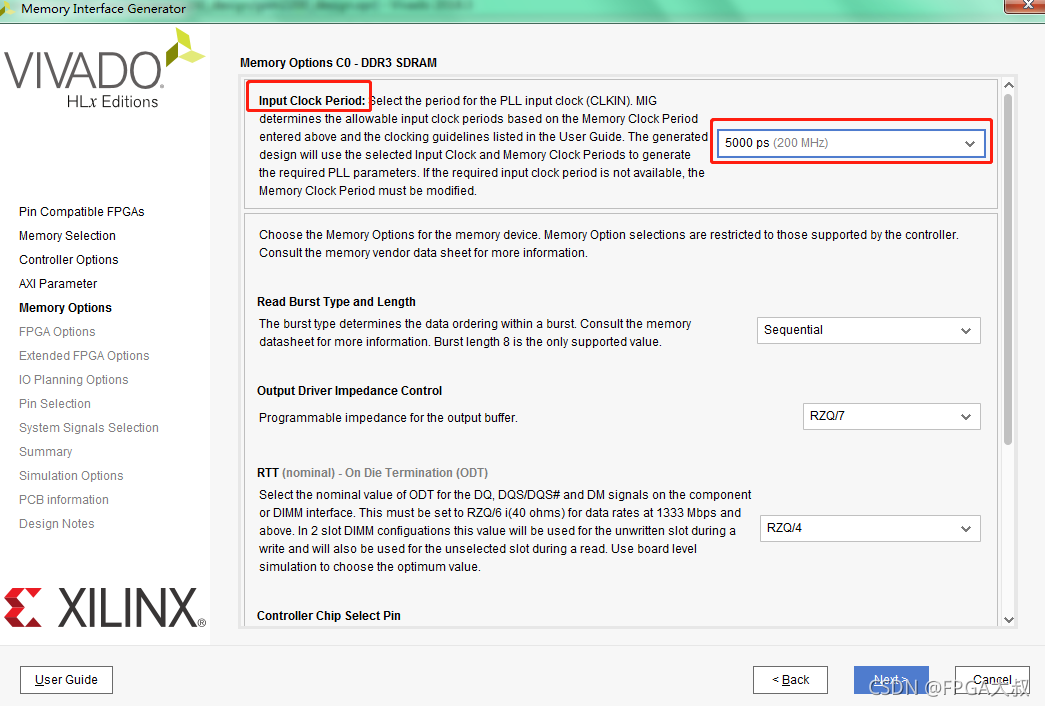

3.3 input clock period

图5. input clock period

input clock period 对应的时钟就是MIG核的系统时钟,由PLL/MMCM输入;对应到例化代码就是:

.sys_clk_i (sys_clk_i ), //系统时钟输入

我们配置MIG核时选择多少M时钟,那么这里就要输入多少M

注:

推荐选择200Mhz,因为参考时钟也是200Mhz,配置的时候参考时钟可以直接使用系统时钟,减少端口信号

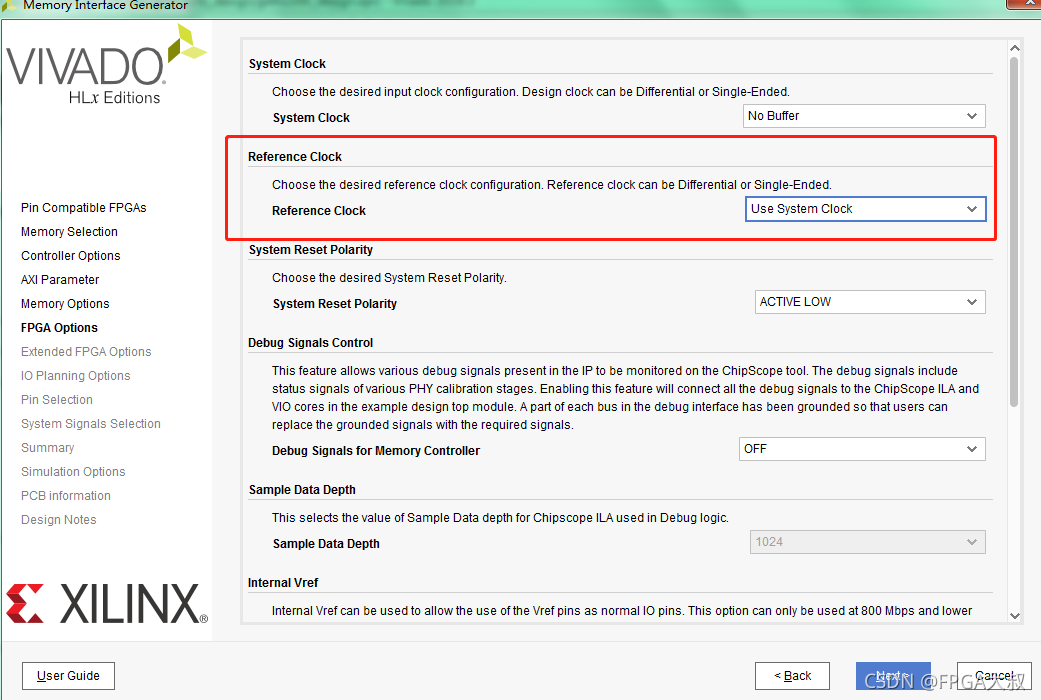

3.4 Reference clock

图6.参考时钟

参考时钟必须为200Mhz!

当我们系统时钟为200M时,参考时钟就可以直接使用系统时钟(use system clock)

四、行业术语

1. 核心频率:核心频率就是DDR物理层(PHY)IO时钟频率,对应到MIG就是第一个配置的“CLOCK PERIOD”,上文我们选择的是800Mhz

2. 工作频率:核心频率* 2 (上下沿)= 1600M核心频率* 2 = 1600M

3. 传输速率:核心频率* 2 = 1600MT/s

4. 带宽:传输速率*位宽 = 1600M * 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s