作者: 小翁同学,文章来源:博客园

前言

使用DSP的方法一般有两种:让综合器自己推断、例化DSP原语。

有的时候为了偷懒或者有的计数器之类的需要跑高速,则可以让计数器也使用DSP实现。

语法:(*use_dsp=“yes”*)

流程

1.编写代码测试,一个乘法器加一个cnt计数器,直接在模块头使用语法规则。

`timescale 1ns/1ps

(*use_dsp = "yes"*)module mul_test (

input i_clk ,

input [17:0] i_mul_a ,

input [17:0] i_mul_b ,

output [35:0] o_mul_result,

output [15:0] o_cnt

);

reg [15:0] r_cnt = 'd0;

always @(posedge i_clk)

begin

r_cnt <= r_cnt + 'd1;

end

assign o_cnt = r_cnt;

reg [17:0] r_mul_a_delay_0 = 18'd0;

reg [17:0] r_mul_a_delay_1 = 18'd0;

reg [17:0] r_mul_b_delay_0 = 18'd0;

reg [17:0] r_mul_b_delay_1 = 18'd0;

reg [35:0] r_mul_result_0 = 36'd0;

reg [35:0] r_mul_result_1 = 36'd0;

reg [35:0] r_mul_result_2 = 36'd0;

reg [35:0] r_mul_result_3 = 36'd0;

always @(posedge i_clk)

begin

r_mul_a_delay_0 <= i_mul_a;

r_mul_a_delay_1 <= r_mul_a_delay_0;

r_mul_b_delay_0 <= i_mul_b;

r_mul_b_delay_1 <= r_mul_b_delay_0;

end

always @(posedge i_clk)

begin

r_mul_result_0 <= r_mul_a_delay_1 * r_mul_b_delay_1;

end

always @(posedge i_clk)

begin

r_mul_result_1 <= r_mul_result_0;

r_mul_result_2 <= r_mul_result_1;

r_mul_result_3 <= r_mul_result_2;

end

assign o_mul_result = r_mul_result_3;

endmodule // end the mul_test model

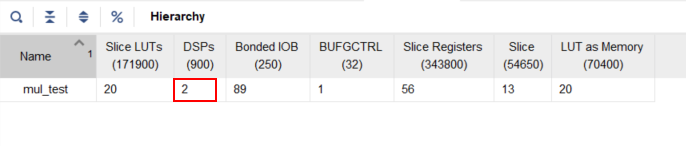

2.综合适配看看结果:可以看到使用了2个DSP块。

如果只是乘法使用DSP实现的话,在结果寄存器添加语法规则即可。

(*use_dsp = "yes"*)reg [35:0] r_mul_result_0 = 36'd0;

以上。