本文转载自: 硬码农二毛哥微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

JTAG 到 AXI Master 简介

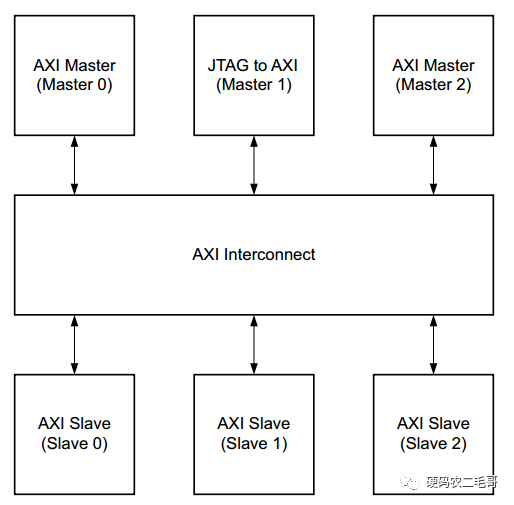

JTAG to AXI Master IPAXI Master驱动AXI事务。JTAG to AXI Master加入AXI Interconnect,可以与Slave0、Slave1和Slave2通信。支持AXI4和AXI4-Lite协议,下面以JTAG to AXI Master调试AXI BRAM 控制器举例说明 JTAG 到 AXI Master 的使用方法。

环境问题

将 AXI Master 加入硬件接口,JTAG 到 AXI Master 与 AXI Interconnect 相同的时钟与主控器连接。AXI Interconnect 的连接 AXI BRAM 控制器。

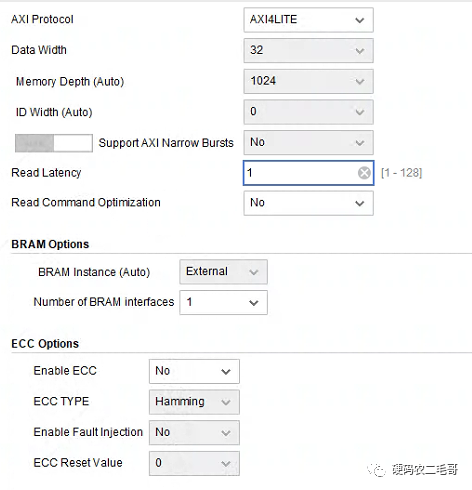

AXI BRAM 控制器设置如下:

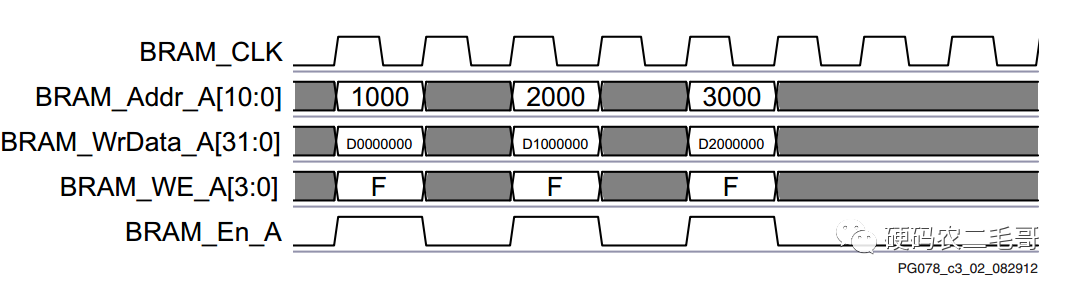

设置AXI BRAM Controller输出端口:

AXI BRAM Controller在内存中地址:

AXI BRAM Controller 磨损

写一句

读写

在PL端加入书写文字。

AXI4-Lite 读写

在 TCL 指令发送,通过查看指令是否正常。

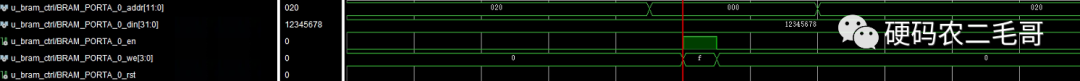

创建 AXI 事务,写入 32 位数据

create_hw_axi_txn abc [get_hw_axis hw_axi_1] -address 80001000 -data 12345678 -type write

run_hw_axi abc

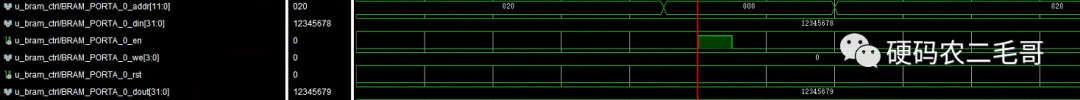

创建AXI交易,读取32位数据

create_hw_axi_txn def [get_hw_axis hw_axi_1] -address 80001000 -type read

run_hw_axi abc

AXI4学习

本次设计中采用AXI4-Lite协议,当选择AXI4协议时,读写指令如下:

写操作

往64bit地址,写入128bit数据。

create_hw_axi_txn wr_txn64 [get_hw_axis hw_axi_1] -address 0000000000000000 -data

{11111111_22222222_33333333_44444444_55555555_66666666_77777777_88888888

- type

读操作

64位地址,写入1个28位数据。

create_hw_axi_txn rd_txn64 [get_hw_axis hw_axi_1] -address 0000000000000000 -len 8

-size 32-type 读取