本文转载自:FPGA技术实战

注:本文由作者授权转发,如需转载请联系作者本人

引言:Vivado®Design Suite提供了几种可能影响I/O和时钟规划的器件规划功能。例如,FPGA配置方案、约束、配置电压方式都会影响I/O和时钟规划。或者,定义与封装兼容的其他器件,以便在最终设计需要时更改FPGA器件时,可以实现无缝衔接。建议在时钟和I/O规划前定义这些特殊的属性。

1.1 定义兼容性器件

您可以为设计选择兼容的FPGA,以便在必要时将设计重新定位到其他Xilinx®器件。Vivado工具在与当前目标部件相同的封装中选择兼容的Xilinx设备,以尽可能多地保留I/O分配。这可确保I/O引脚分配在选定的备用器件中可用。定义替代兼容零件,请执行以下操作:

1)建立工程,执行RTL分析或者综合或者实现步骤;

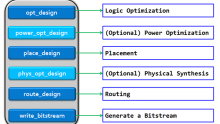

2)上述步骤执行完后,点击任意下图1中任意一个流程;

图1

3)选择Tools > I/O Planning > Set Part Compatibility。

图2、选择兼容性器件

在“设置器件兼容性”对话框中,选择备用器件,然后单击“确定”。

Vivado IDE识别所有选定备用器件共用的管脚,并为并非所有设备共用的管脚指定禁止约束。选择其他替代器件时,可用于放置的管脚数量可能会减少。此外,Vivado IDE自动禁止将信号分配给所选备用设备中的任何未绑定管脚。此时会出现一个对话框,显示禁止的封装PIN数。您可以在封装、封装Pin、和器件窗口中查看。禁止使用的管脚由斜线圆圈图标表示。

另外,在器件选型手册中也会给出器件封装兼容器件选型,只进行器件封装兼容性选型。

图3、器件选型兼容性描述

1.2 设置器件配置模式

由于Xilinx器件配置数据存储在CMOS锁存器中,因此器件每次通电时都必须重新配置。比特流通过特殊模式配置管脚加载到器件中,这些管脚用作多种不同配置模式的接口。通过在专用输入引脚上设置适当的电压水平来选择特定的配置模式。

每个配置模式都有一组相应的接口引脚,这些引脚跨越器件上的一个或多个I/O Bank。Bank0包含专用配置引脚,并且始终是每个配置接口的一部分。UltraScale™和UltraScale+™中的Bank65和7系列器件中的Bank14和15包含用于各种配置模式的多功能管脚。

设置配置模式和查看配置信息可以执行以下操作步骤:

1)建立工程,执行RTL分析或者综合或者实现步骤。

图4、配置选择

2)选择对应的配置模式。

启用配置模式复选框以设置该配置模式。设置配置模式时:

-相关的I/O引脚显示在Package pins窗口的Config列中。

-保存设计时将创建以下约束:

set_property BITSTREAM.CONFIG.PERSIST NO [current_design]

set_property CONFIG_MODE

单击配置模式打开一个对话框,您可以在其中查看信息,包括描述、配置图和指向更多信息的链接。单击“打印”以打印配置图。

图5、Master SPI×4配置模式

启用禁止将配置管脚用作用户I/O,并在配置后保持,以确保管脚在配置后用作配置管脚,而不是用作通用I/O。选择此选项时,保存设计时将创建以下约束:

set_property BITSTREAM.CONFIG.PERSIST YES [current_design]

图6、禁止将配置管脚用作用户I/O

注意:JTAG配置模式为始终选择配置模式。除JTAG配置模式外,您还可以选择一种配置模式。

3)配置模式选择完成后,执行File > Save Constraints,将当前配置保存到.xdc约束文件中。

1.3 设置器件约束

在器件约束窗口(图2-3)中,您可以设置约束,包括DCI_CASCADE和INTERNAL_VREF。Xilinx器件具有可配置的SelectIO™接口,支持许多标准接口的接口驱动程序和接收器。具有包括驱动强度和转换率的可编程控制、使能数字控制阻抗(DCI)的片上终端,以及内部生成参考电压(INTERNAL_VREF)的能力。

图7、器件约束窗口

根据I/O标准,Xilinx DCI可以控制驱动器的输出阻抗,也可以为驱动器、接收器或两者添加并行终端,目的是精确匹配传输线的特性阻抗。DCI主动调整I/O Bank内的阻抗,以校准VRN和VRP引脚上的外部精密参考电阻器。这可以补偿由于工艺变化、温度或电源电压变化引起的I/O阻抗变化。DCI在每个I/O Bank中使用两个多用途参考引脚来控制驱动器的阻抗或组中所有I/O的并行端接值。

带有差分输入缓冲的单端I/O标准需要参考电压VREF。当I/O Bank内需要VREF时(例如DDR3 I/O接口),请使用该Bank的以下引脚作为VREF电源输入:

或者,可以使用INTERNAL_VREF约束生成内部VREF。使用内部参考电压可以消除在PCB上提供特定VREF供电轨的需要,并且可以在给定I/O组中释放多用途VREF引脚,用于其他I/O端口分配。每个I/O Bank都有一个VREF平面,每个Bank都可以将可选的INTERNAL_VREF设置为整个Bank电压标准。

注意 :当是使用INTERNAL_VREF内部参考电压时,与外部参考VREF相比,器件的性能可能会有所不同,例如DDR内存接口。

1)产生DCI_CASCADE约束

选中需要设置DCI_CASCADE约束的Bank,右键选择Add DCI_CASCADE,弹出对话框中选择主Bank。

图8、设置DCI_CASCADE约束

.xdc约束文件设置DCI_CASCADE约束:

set_property DCI_CASCADE {34 35} [get_iobanks 33]

注意:当使用这个Tcl命令时,get_iobanks指定主Bank。在本例中,34和35是从Bank,33是主Bank。

2)修改或移除DCI_CASCADE约束

要修改DCI级联,在设备约束窗口中执行以下任一操作。

图9、移除DCI_CASCADE约束

3)产生INTERNAL_VREF约束

Xilinx器件可以通过启用INTERNAL_VREF约束,选择性地使用内部生成的参考电压。内部生成消除了在PCB上提供特定VREF供电导轨的需要,并将给定I/O Bank中的多用途VREF引脚释放出来,用作普通I/O引脚。

图10、产生INTERNAL_VREF约束

要创建INTERNAL_VREF约束,请将I/O Bank拖放到设备约束窗口中所需的电压文件夹(例如,0.75V或0.9V)。

.xdc约束文件设置INTERNAL_VREF约束:

set_property INTERNAL_VREF 0.7 [get_iobanks 65]

set_property INTERNAL_VREF 0.84 [get_iobanks 69]

延伸阅读:Xilinx 7系列SelectIO结构之DCI(动态可控阻抗)技术(一)

1.4 设置配置Bank管脚电压选择管脚

配置Bank电压选择管脚(CFGBVS)在VCCO_0和GND之间参考。CFGBVS引脚必须设置为高或低,以确定Bank0中引脚的I/O电压支持。在Vivado工具中,可以使用Tcl命令将CFGBVS连接信息设置为VCCO或GND。您可以将配置电压或VCCO_0电压设置为1.5、1.8、2.5或3.3。基于这些设置,7系列设备的DRC在Bank0、14和15上运行。对于UltraScale设备,DRC在Bank0和65上运行。

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

默认情况下,CFGBVS属性为空。Vivado工具检查CFGBVS属性是否设置为VCCO或GND。如果CFGBVS属性有值,Vivado工具会检查CONFIG_MODE属性。DRC是根据Bank IO标准和CFGBVS配置电压设置发布的。

当您导出到CSV文件时,Vivado工具会根据CONFIG_MODE属性的设置为相关Bank(7系列器件:Bank0、14和15;基于UltraScale体系结构的器件:存Bank0和65)提供VCCO绑定信息。例如,如果使用JTAG/Boundary Scan,CFGBVS为GND,配置_电压为3.3,则工具会发出严重警告:DRC CFGBVS-4。这表明CONFIG_VOLTAGE设置为3.3,必须改为设置为VCCO,其值为1.8。对于UltraScale+器件,无法手动设置CFGBVS或CONFIG_VOLTAGE。默认情况下,CFGBVS设置为GND,CONFIG_VOLTAGE设置为1.8V。