本文转载自: FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

xilinx提供了丰富的原语,可以将之看成FPGA开发可以使用的库函数,原语在FPGA中具有与之对应的硬件逻辑单元,但也注意,不同的FPGA的原语可能会有所不同,但常用的原语不同器件相似度极高。按照功能,主要分为:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特组件。虽然不管哪个组件都很重要,但必须选择一个的话,我会选择时钟组件。下面就对时钟组件的原语学习一波。

时钟组件包括各种全局时钟缓冲器、全局时钟复用器以及高级数字时钟管理模块,主要说下前两者,高级数字时钟管理模块PLL复杂不少,写的话,会很长,其次,这个可以通过时钟IP来调用即可,如果想详细了解的话,可以看官方文档ug572。常遇到的比如:MMCME4_ADV、PLLE4_ADV、MMCME4_BASE、PLLE4_BASE等。后面原语以UltraScale系列器件为例。

下面对几个常用时钟组件进行简单学习,其他类似。

1. BUFG

BUFG具有高扇出驱动能力,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,比如常用到的复位信号和时钟使能信号。综合器一般会自动推断添加,当然,也可以自己手动添加。BUFGCE和BUFGCE_1实际就是在BUFG的基础上增加了时钟使能控制。

BUFG BUFG_inst (

.O(O), // 1-bit output: Clock output.

.I(I) // 1-bit input: Clock input.

);

2. BUFGMUX

通俗来说就是一个时钟选择器,选择两个输入时钟I0或I1中的一个作为全局时钟,当S为0时,选择I0,否则选择I1。对于BUFGMUX_1,当S为1时,选择I0,否则选择I1。

BUFGMUX #(

.CLK_SEL_TYPE("SYNC") // ASYNC, SYNC

)

BUFGMUX_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

3. BUFGCTRL

可以在两个异步时钟之间切换,默认是下降沿触发,但可以通过更改INIT_OUT参数调整成上升沿触发。

BUFGCTRL #(

.INIT_OUT(0), // Initial value of BUFGCTRL output, 0-1

.PRESELECT_I0("FALSE"), // BUFGCTRL output uses I0 input, FALSE, TRUE

.PRESELECT_I1("FALSE"), // BUFGCTRL output uses I1 input, FALSE, TRUE

// Programmable Inversion Attributes: Specifies built-in programmable inversion on specific pins

.IS_CE0_INVERTED(1'b0), // Optional inversion for CE0

.IS_CE1_INVERTED(1'b0), // Optional inversion for CE1

.IS_I0_INVERTED(1'b0), // Optional inversion for I0

.IS_I1_INVERTED(1'b0), // Optional inversion for I1

.IS_IGNORE0_INVERTED(1'b0), // Optional inversion for IGNORE0

.IS_IGNORE1_INVERTED(1'b0), // Optional inversion for IGNORE1

.IS_S0_INVERTED(1'b0), // Optional inversion for S0

.IS_S1_INVERTED(1'b0), // Optional inversion for S1

.SIM_DEVICE("ULTRASCALE_PLUS") // ULTRASCALE, ULTRASCALE_PLUS

)

BUFGCTRL_inst (

.O(O), // 1-bit output: Clock output

.CE0(CE0), // 1-bit input: Clock enable input for I0

.CE1(CE1), // 1-bit input: Clock enable input for I1

.I0(I0), // 1-bit input: Primary clock

.I1(I1), // 1-bit input: Secondary clock

.IGNORE0(IGNORE0), // 1-bit input: Clock ignore input for I0

.IGNORE1(IGNORE1), // 1-bit input: Clock ignore input for I1

.S0(S0), // 1-bit input: Clock select for I0

.S1(S1) // 1-bit input: Clock select for I1

);

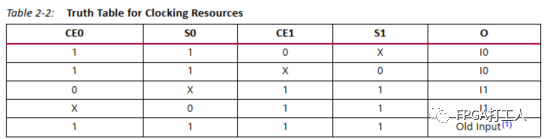

其工作真值表如下,具体使用时,xilinx建议通过控制S切换时钟,原因是CE切换时,时钟变化速度过快,容易造成建立/保持时间违规。

4. BUFGCE_DIV

最主要的可以将输入时钟进行1-8倍的分频操作。CLR是复位信号,CE是使能信号。有一个点需要注意,奇数分频时,占空比不是50%。

BUFGCE_DIV #(

.BUFGCE_DIVIDE(1), // 1-8

// Programmable Inversion Attributes: Specifies built-in programmable inversion on specific pins

.IS_CE_INVERTED(1'b0), // Optional inversion for CE

.IS_CLR_INVERTED(1'b0), // Optional inversion for CLR

.IS_I_INVERTED(1'b0), // Optional inversion for I

.SIM_DEVICE("ULTRASCALE_PLUS") // ULTRASCALE, ULTRASCALE_PLUS

)

BUFGCE_DIV_inst (

.O(O), // 1-bit output: Buffer

.CE(CE), // 1-bit input: Buffer enable

.CLR(CLR), // 1-bit input: Asynchronous clear

.I(I) // 1-bit input: Buffer

);