本文转载自:FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

在有些情况下,开发人员只有综合后的DCP文件和对应的约束XDC及各个IP,并没有综合之前的code,这种情况下vivado可以通过tcl脚本跑完实现并得到bit。前段时间因为需要,简单研究了一下。

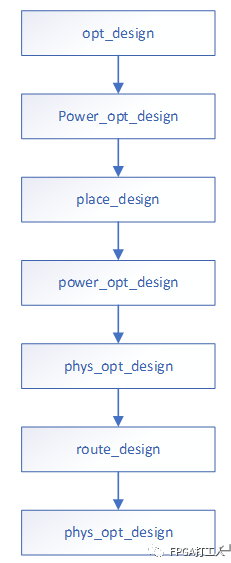

在vivado下,实现由多个子步骤构成的:

其中place_design和route_design是必须的,其他都是可选的。

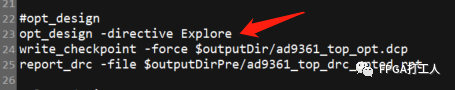

每个子环节的实现策略是可选的,是通过-directive参数提供设置,具体实现如下:

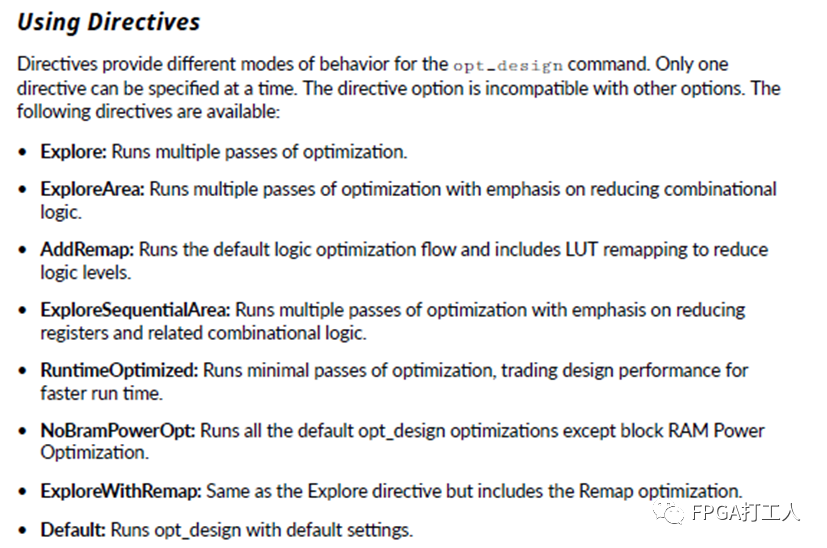

具体的参数可在xilinx官方提供ug904文档中查到,这边只列举一下opt_design可以使用的策略。

具体实现流程如下:

步骤1:读取综合后的dcp文件;

步骤2:读取实现对应的xdc文件;

步骤2:读取project用到的所有ip文件;

步骤4:设置目标device和link netlists;

步骤5:运行实现各个子环节的tcl命令并配置策略;

步骤6:生成bit;

当然,在实现过程中,可以将实现各个子环节运行后的报告打印出来,并生成不同的dcp文件,具体的tcl脚本文件和ug904可以在后台回复“implementation”获得,若失效在评论中说明,及时更新。