本文转载自: FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

BUFGMUX可能使用Xlinx FPGA器件的都有了解,但从使用角度考虑,做FPGA产品开发时,可能使用比较少,但做FPGA原型验证可能就比较多了。

BUFGMUX在逻辑互斥情况下使用其一般的约束方法可参考之前的文章:

最近遇到的一个问题:

IC设计的某个功能在一定的时间内需要来回切换两个时钟,看切换的时差间隔和设定的差距有多大,而这两个时钟一个是32K,一个16M,结果在FPGA验证环节发现有一定的delay,这个delay值与设定的差距比较大,并且也是稳定的一个delay值。刚开始先怀疑到了RTL那边,但实际问题是出在BUFGMUX上。

其实主要和BUFGMUX的属性参数有关:

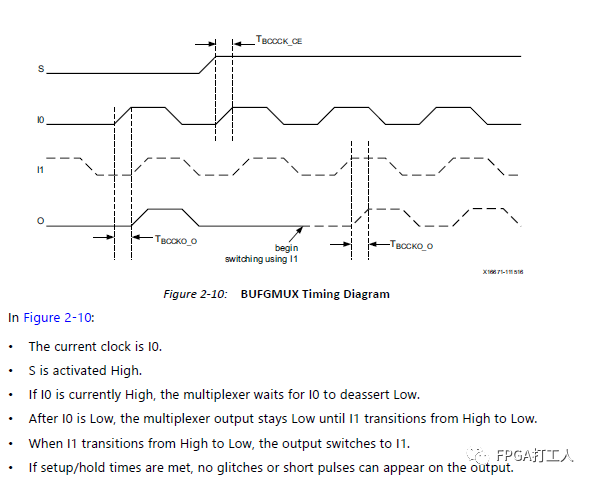

简单说下属性参数。其默认是SYNC,在该模式下时,sel信号变化后,时钟不会立即生效,会简单进行一个相位的判断,在合适的时机做一个切换工作,ug572中也有提到:

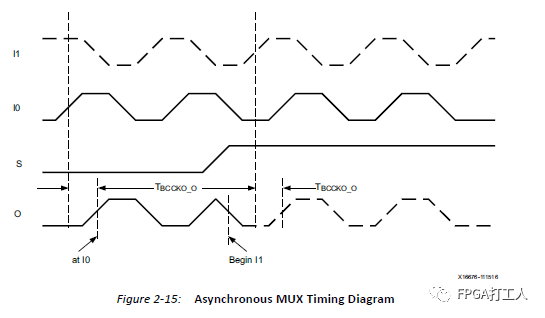

而在ASYNC模式下,时钟的切换就会立马生效,但这可能在切换的那一瞬间,时钟会出现不稳定的情况,所以在该模式下,要考虑到这个因素,

ug572也有提到:

而在该问题的ASIC行为中,时钟切换是立马生效的,所以应该选择ASYNC模式。

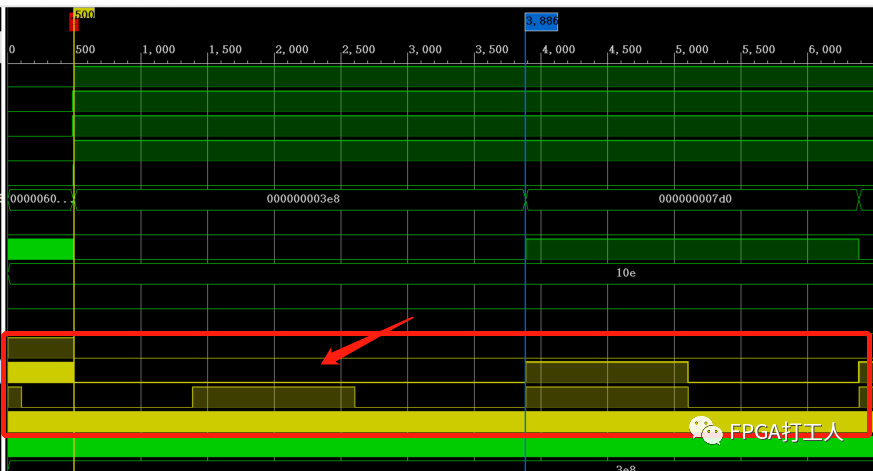

下面是抓取到的波形行为(采样时钟使用的是80M,后面黄色部分,第一个为选择信号,第二个MUX的输出信号,第三个是32K,第四个是16M):

第一张图是BUFGMUX设置为SYNC,32K切换到16M时抓取到的信号,根据波形计算,32K上升沿到16M上升沿波形时delay为15.375us。

第二张图是BUFGMUX设置为SYNC,16M切换到32K时抓取到的信号,根据波形计算,16M的上升沿切换到32K上升沿波形时delay为42.325us,这其中也有clk自己等待跳转高电平的时间。

第三张图是BUFGMUX设置为ASYNC,32K切换到16M时抓取到的信号,根据波形,的确立马生效了,但生效那一刻会有个毛刺。

第四张图是BUFGMUX设置为ASYNC,16M切换到32K时抓取到的信号,根据波形,的确立马生效了。