作者:孤独的单刀,文章来源:CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

1、什么是BRAM

RAM是什么?RAM就是一张存储表,可写、可读。只要提供地址信息与数据,就可以往指定的地址写入数据,此谓存入信息;同样的,只要提供地址信息,就可以从指定的地址将存储的信息读出来,此谓读取信息。

那BARAM又是什么?BRAM,Block RAM,俗称 块RAM。BRAM是相对DRAM来说的,DRAM是分布式RAM,是由遍布FPGA全片的逻辑资源LUT构成的RAM(所以叫分布式RAM)。而BRAM则是一整块,完整地固定在FPGA内部的嵌入式资源构成的RAM(所以叫块RAM)。

2、BRAM的组成

每个BRAM资源可以存储36Kb的数据,这意味着一个最小的BRAM资源是36Kb。但其实36Kb的BRAM还可以切割成2个18Kb的BRAM,这是BRAM的最小实现形式。

这是什么意思呢?打个比方,如果你希望用BRAM来存储50Kb的数据(先别管深度和位宽),那么最后消耗的BRAM资源应该 = 1个36Kb的BRAM + 1个18Kb的BRAM,尽管这会浪费4Kb(36+18-50=4)的存储空间。

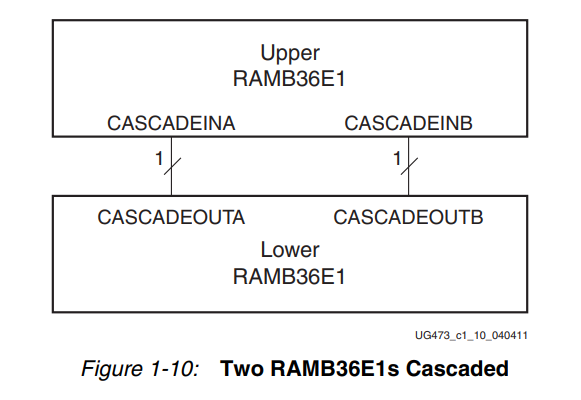

2个相邻的BRAM可以级联配成72Kb的BRAM,这也是我们使用大容量BRAM的实现基础。

每个36Kb的BRAM根据位宽与深度的不同,可以配成成如下形式(深度 × 位宽):32K x 1, 16K x 2, 8K x 4, 4K x 9, 2K x 18, 1K x 36, 512 x 72

每个18Kb的BRAM根据位宽与深度的不同,可以配成成如下形式(深度 × 位宽):16K x 1, 8K x2 , 4K x 4, 2K x 9, 1K x 18 ,512 x 36

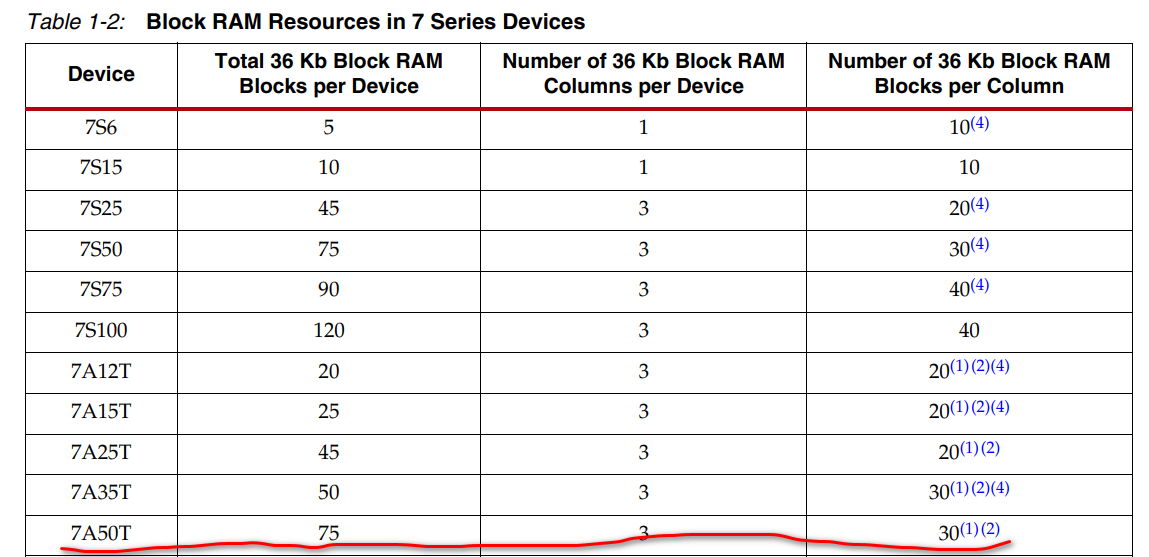

不同类型的FPGA中BRAM的数量是不相同的,BRAM的数量也是FPGA选型的一个重要因素。

下表例举了部分FPGA的BRAM数量:

以其中7A50T系列的FPGA为例:可以看到,BRAM资源在其中是按列排布的,一共3列,每列30个,一共就是90个,但是由于GT和PCIE占据了部分位置,所以最终资源数量是75个。

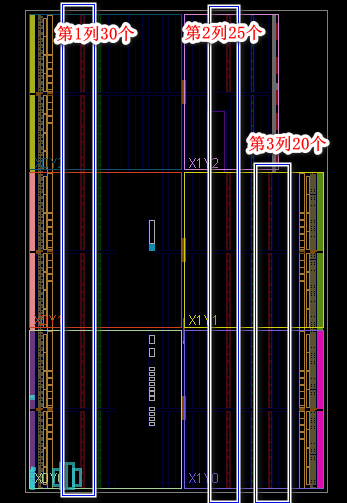

我们用vivado打开该FPGA的device界面:

可以看到:第1列的BRAM数量是30个,第2列25个 ,第3列20个。所以一共是75个BRAM。

3、BRAM的使用

根据不同的需求,可以将BRAM配成成不同的形式。

3.1、RAM

BRAM资源可以实现不同形式的RAM。这听着就一句废话,BRAM不做RAM还能做什么?不好意思,还能做ROM,也还能做FIFO。

关于RAM部分可以参考:

从底层结构开始学习FPGA----RAM IP核及其关键参数介绍

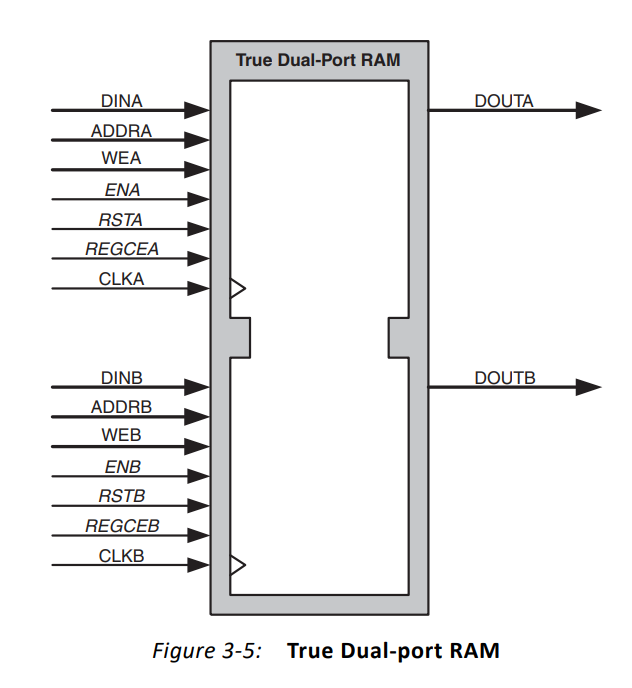

(1)真双口RAM(True Dual-port RAM)

有两个独立的端口A和端口B,2个端口都可以读、写。

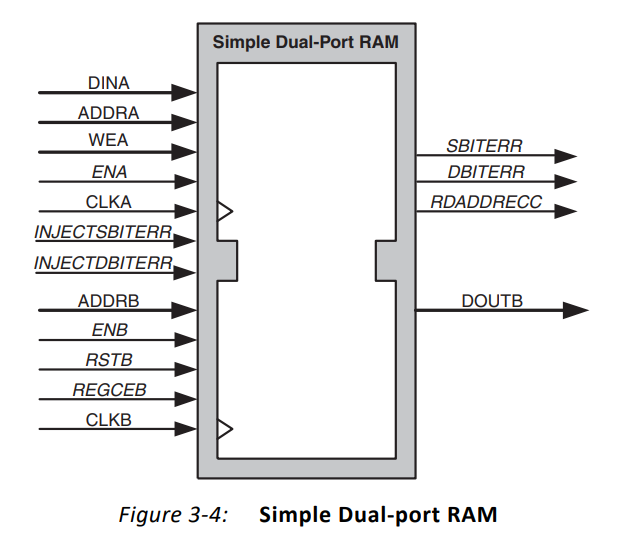

(2)简单双口RAM(Simple Dual-port RAM)

有两个独立的端口A、B,其中一个端口只读,另一个端口只写。

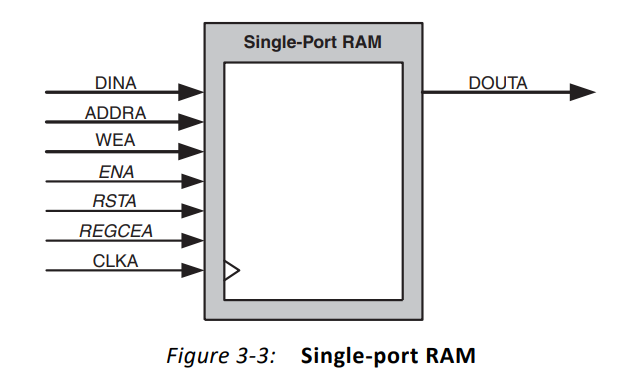

(3)单口RAM(Single-port RAM)

只有一个端口,可读可写,但无法同时进行。

3.2、ROM

ROM可以看做是一个无法写入(初始化不算)的RAM,所以BRAM能实现RAM,那肯定也能实现ROM。

关于ROM部分可以参考:

从底层结构开始学习FPGA----Xilinx ROM IP的定制与测试

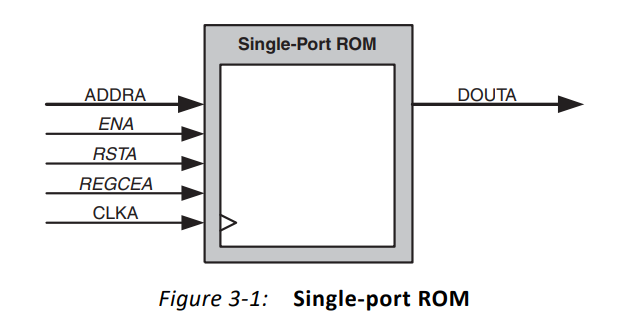

(1)单端口 ROM

不可实现写操作,只可使用一个端口实现读操作。

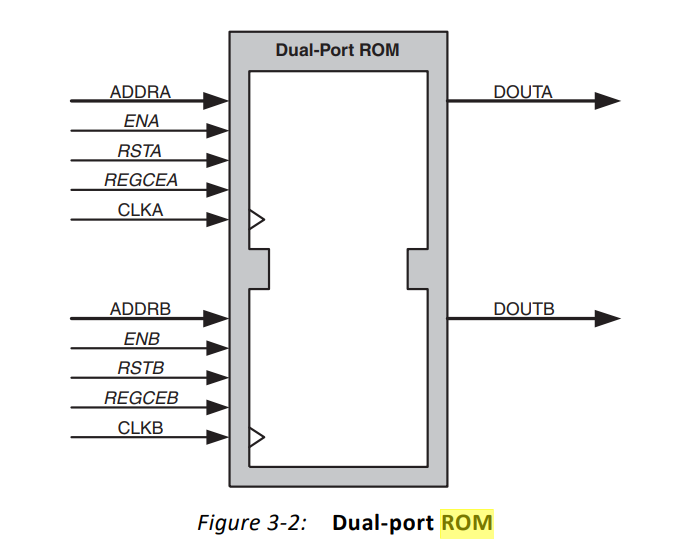

(2)双端口ROM

不可实现写操作,可以使用两个端口实现读操作,两个端口读取数据的位宽可以不同,但必须是整数倍关系。

3.3、FIFO

FIFO本质上也是用RAM构成的,不过是在外围构建了读写指针逻辑,让其实现先进先出的功能,而无法根据地址进行读写。

关于FIFO部分可以参考:

从底层结构开始学习FPGA----FIFO IP核及其关键参数介绍

从底层结构开始学习FPGA----FIFO IP的定制与测试

根据读写时钟的是否一致性,可以将FIFO分为两个大类:

同步FIFO,Synchronize fifo

异步FIFO,Asynchronize fifo

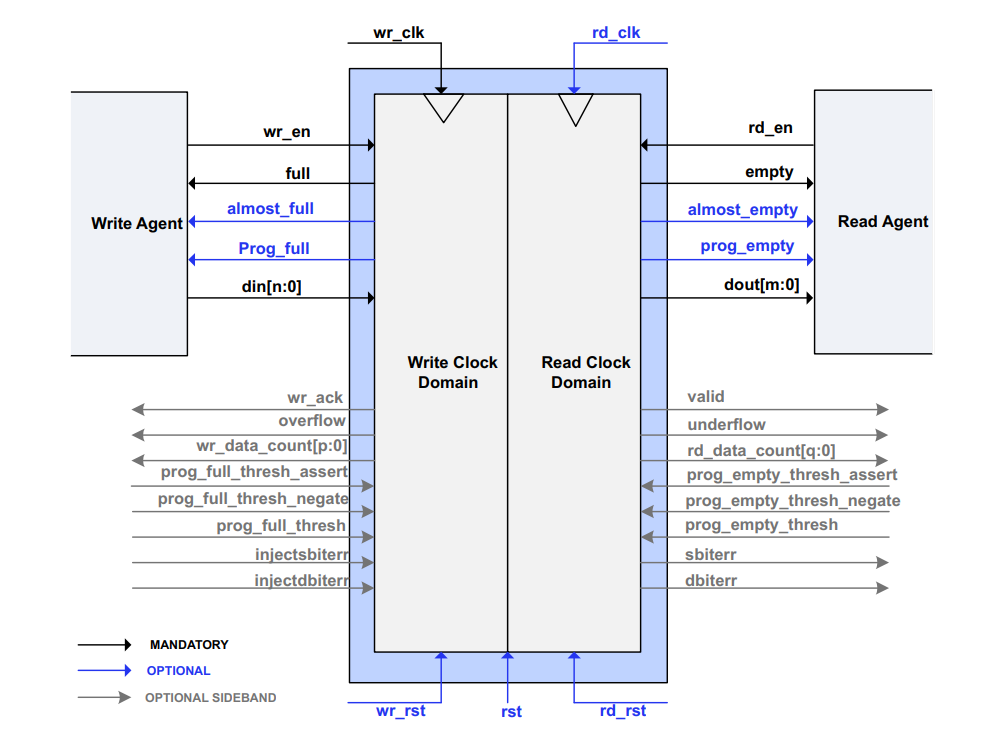

下图是一张异步FIFO的组成图,标识了异步FIFO的不同读写时钟域。一旦读写时钟域一致,那么它就变成了一个同步FIFO。

4、一些需要注意的

BRAM资源并不复杂,一般来讲,在实际使用过程中,即使不了解BRAM,也不影响我们调用其来实现RAM\ROM\FIFO。但是下面这些注意事项,了解一下还是可以提高开发效率的。

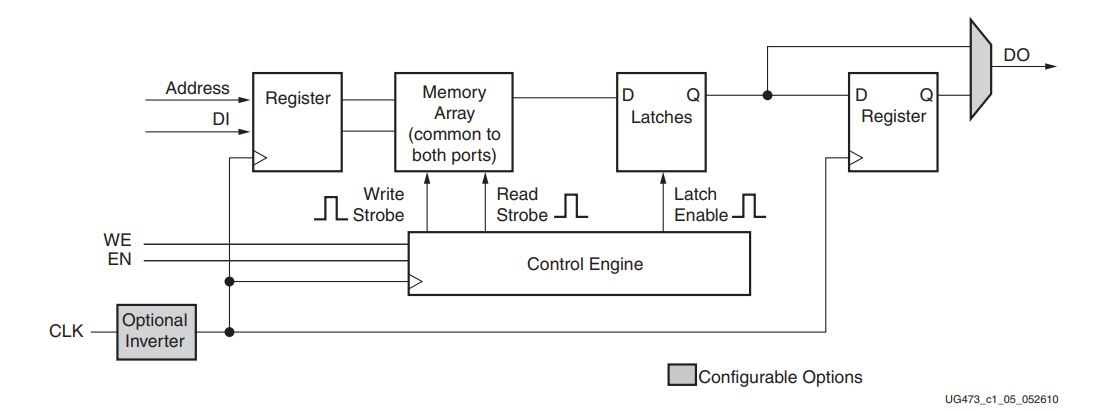

4.1、自带的输出寄存器

一般来讲,在数据的输出口添加一个寄存器虽然会增加延迟latency,但可以切割组合逻辑路径从而改善时序。每个BRAM资源内部在输出端都提供了一个可选的输出寄存器,把这个寄存器用上,不光可以省下SLICE里面的寄存器资源,而且由于这个寄存器在BRAM内部,所以延迟也小很多。

4.2、BRAM级联

7系列FPGA的2个相邻的BRAM,可以级联组成72Kb的BRAM,而不需要消耗多余的逻辑资源和布线资源。如下:

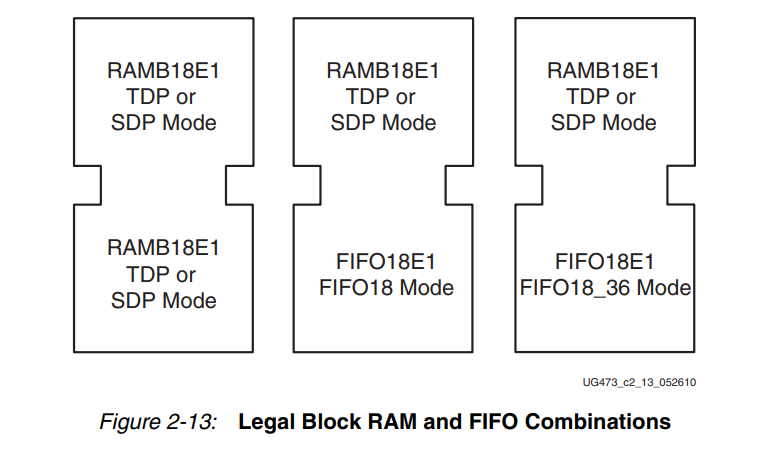

4.3、FIFO的实现组合

每个36K的BRAM资源可以配置成2个18K的BRAM资源,还可以配置成1个18KRAM + 1个18KFIFO的形式,但是FIFO只能是36Kb下面的那个部分。如下:

5、总结与参考

BRAM资源是FPGA底层内嵌的存储资源

每一块BRAM是36Kb大小,同时还可以配置成2个18Kb大小的BRAM

相邻的BRAM可以级联组成更大容量的BRAM

BRAM资源可以用来实现各种RAM/ROM/FIFO