本文转载自:孤独的单刀的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

1、概述

锁相环 (phase-locked loop,PLL),是一种控制反馈电路。PLL对时钟网络进行系统级别的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能。MMCM是混合模式时钟管理器,相当于能够进行精准相移的PLL。(PLL为模拟电路,动态调相位数字电路)。

混合模式时钟管理器 (mixed-mode clock manage,MMCM) 的官方解释:This is a PLL with some small part of a DCM tacked on to do fine phase shifting (that’s why its mixed mode - the PLL is analog, but the phase shift is digital)。就是MMCM是在PLL的基础上增加了相位动态调整功能,使得纯模拟电路的PLL混合了数字电路设计,所以叫Mixed Mode。某种程度上,可以将PLL看做是MMCM的一个功能子集。

MMCM、PLL的功能可以总结为3点:

2、组成

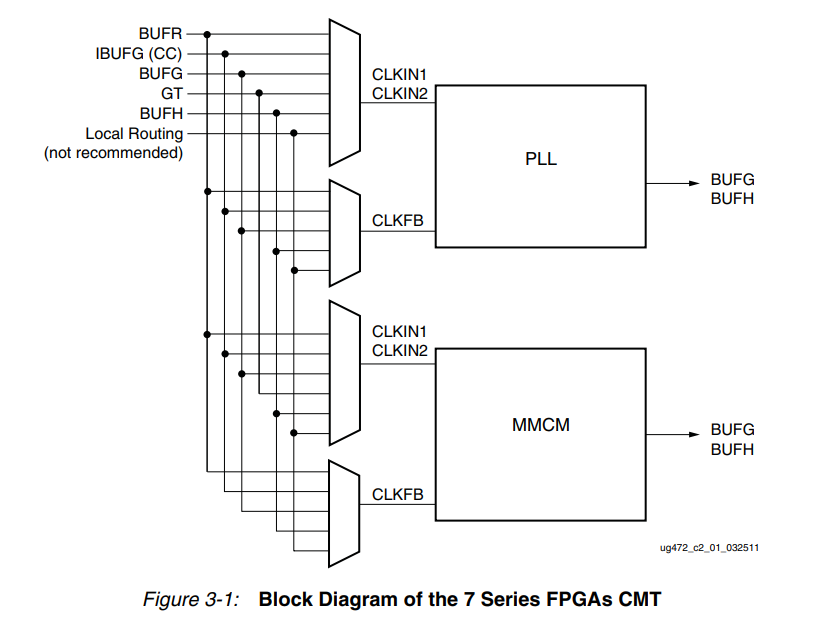

在 7 系列 FPGA 中,每个时钟管理块 (CMT) 都包括一个MMCM和一个PLL。其大致框图如下:

PLL和MMCM都可以有两个时钟输入(一般情况用一个足够了),输入的时钟可以是来自:

同时还需要选择一个时钟输入到时钟反馈引脚CLKFB,作为系统的反馈时钟输入。

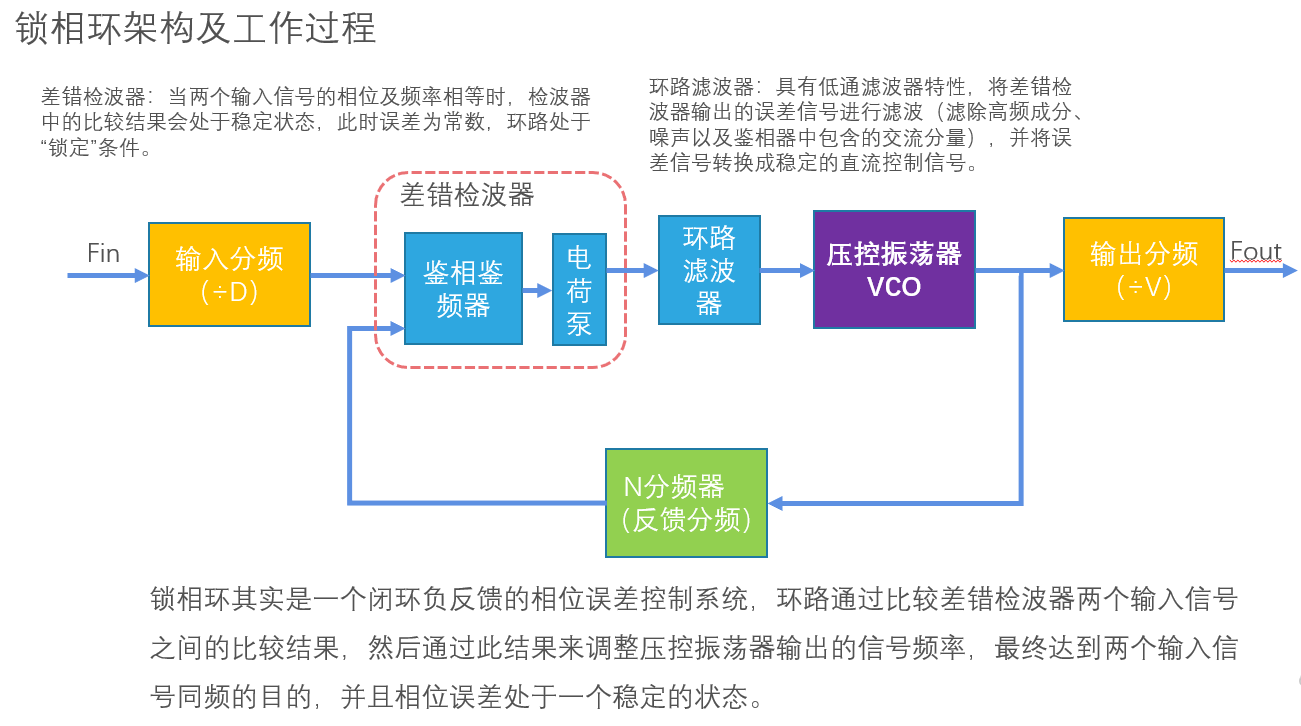

下图详细说明了PLL的工作原理,本质上就是一个反馈的相位、频率控制系统。

首先需要参考时钟(ref_clk)通过鉴频(FD)鉴相器(PD)和需要比较的时钟频率进行比较,我们以频率调整为例,如果参考时钟频率等于需要比较的时钟频率则鉴频鉴相器输出为 0,如果参考时钟频率大于需要比较的时钟频率则鉴频鉴相器输出一个变大的成正比的值,如果参考时钟频率小于需要比较的时钟频率则鉴频鉴相器输出一个变小的正比的值。

频鉴相器的输出连接到环路滤波器(LF)上,用于控制噪声的带宽,滤掉高频噪声,使之稳定在一个值,起到将带有噪声的波形变平滑的作用。如果鉴频鉴相器之前的波形抖动比较大,经过环路滤波器后抖动就会变小,趋近于信号的平均值。

经过环路滤波器的输出连接到压控振荡器(VCO)上,环路滤波器输出的电压可以控制 VCO 输出频率的大小,环路滤波器输出的电压越大 VCO 输出的频率越高,然后将这个频率信号连接到鉴频鉴相器作为需要比较的频率。

如果 ref_clk 参考时钟输入的频率和需要比较的时钟频率不相等,该系统最终实现的就是让它们逐渐相等并稳定下来。比如ref_clk 参考时钟的频率是 50MHz,经过整个闭环反

馈系统后,锁相环对外输出的时钟频率 pll_out 也是 50MHz。

倍频是在 VCO 后直接加分频器,ref_clk 参考时钟输入的频率和需要比较的时钟频率经过闭环反馈系统后最终会保持频率相等,而在需要比较的时钟之前加入分频器,就会使进入分频器之前的信号频率为需要比较的时钟频率的倍数,VCO 后输出的 pll_out 信号频率就是 ref_clk 参考时钟倍频后的结果。

分频是在 ref_clk 参考时钟后加分频器,这样需要比较的时钟频率就始终和 ref_clk 参考时钟分频后的频率相等,在 VCO 后输出的 pll_out 信号就是 ref_clk 参考时钟分频后的结果。

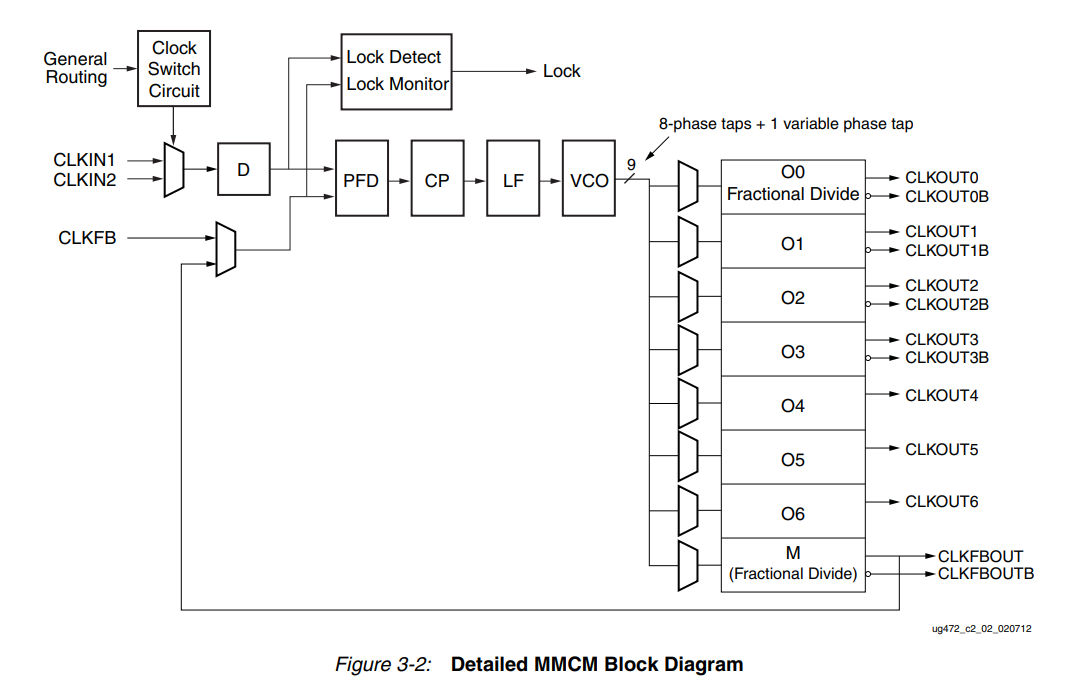

下图是MMCM的结构框图:

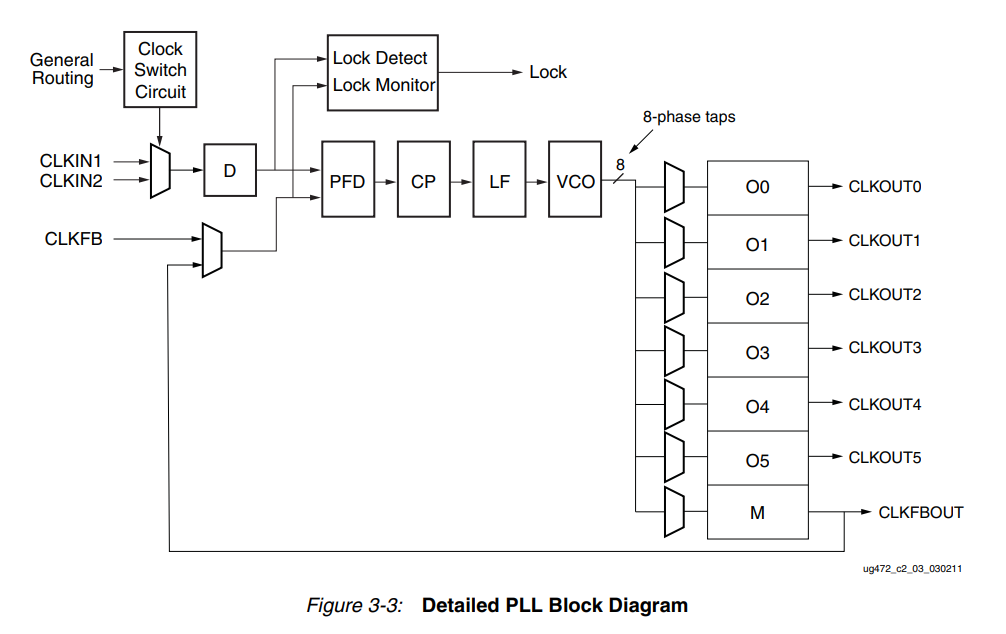

下图是PLL的结构框图(功能少了一些):

其结构与MMCM大体一致,但没有反相输出、分数倍数的除法、精确的动态相位调整以及CLKOUT6。

MMCM、PLL均可实现时钟整数倍的频率综合、去抖、去偏斜,但MMCM还可以实现分数倍的频率综合、反相时钟输出以及动态的时钟相位调整。对于一般的应用,用PLL还是MMCM都区别不大。

3、官方推荐用法

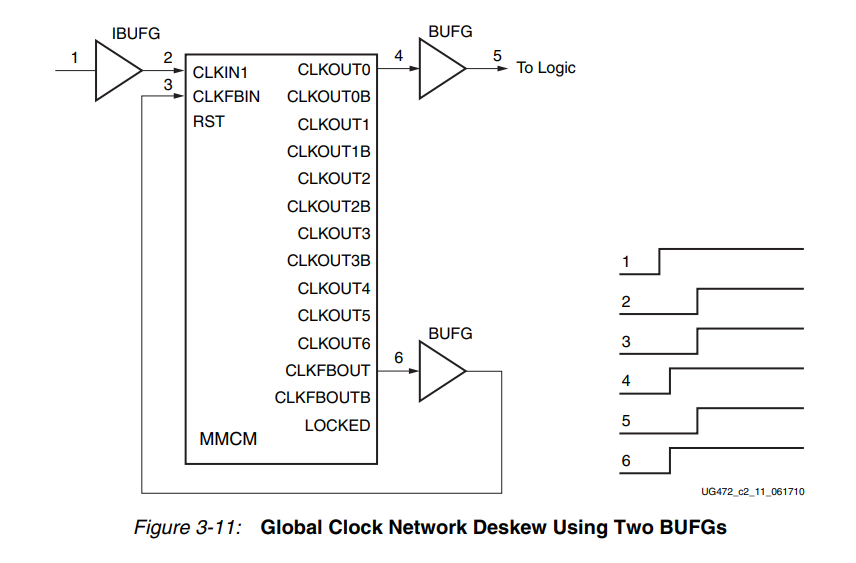

(1)时钟网络去偏斜

最典型的用法,PLL的输入时钟与输出时钟是相位一致的,也就是说去除了时钟偏斜SKEW。坏处是用了2个BUFG,而BUFG在FPGA中一般只有32个,着实宝贵。

右下角的时序图说明了输入时钟2与输出时钟5的相位是已知、对齐的。4和6都是输出时钟,相位是一致的。2是输入,3是负反馈输入,2、3也是一致的。4到5经过一个BUFG,6到3经过一个BUFG,而BUFG通常延时一致,所以5、3相位一致。5=3,3=2,所以5=2,即输出5与输入2相位一致,这样就消除了时钟偏斜。

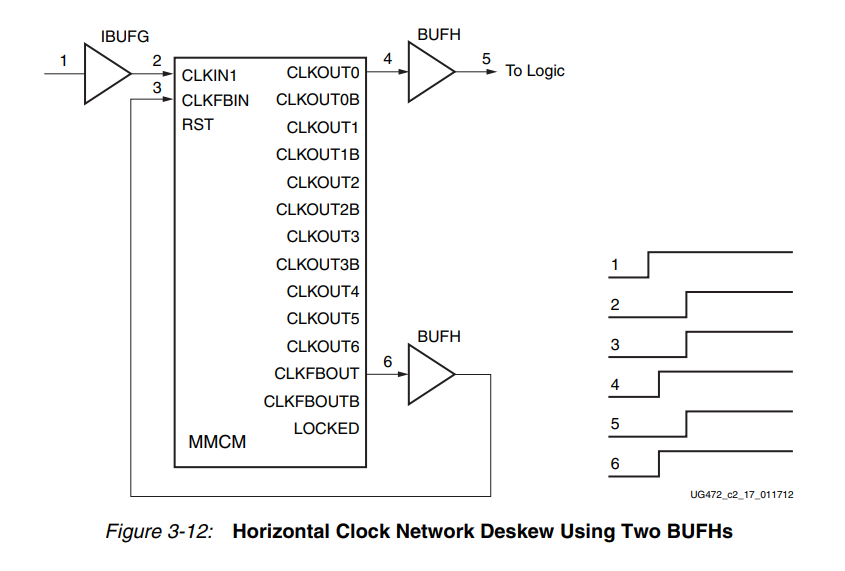

下图是一个BUFH的例子,BUFH不是全局时钟,只能应用于相邻的时钟区域,所以应用范围不如上面的BUFG,但是原理是一样的。

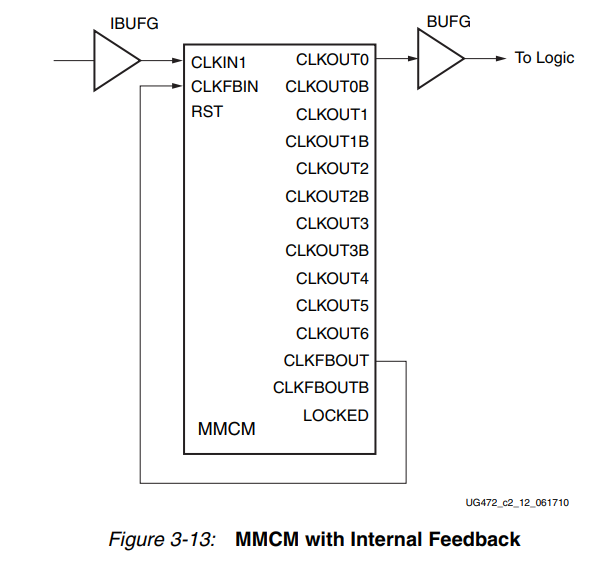

(2)内部反馈

这种方法与上面方法相比,去除了反馈环路上的BUFG,直接走线接入反馈时钟引脚。这种方法性能会比上面的方法好,性能提高是因为反馈时钟不受内核电源噪声的影响,它从不通过由该电源供电的模块。但是这样也失去了输入时钟域输出时钟的相位对齐关系,所以它比较适用于高精度的频率综合,而对相位关系不太关注的应用。

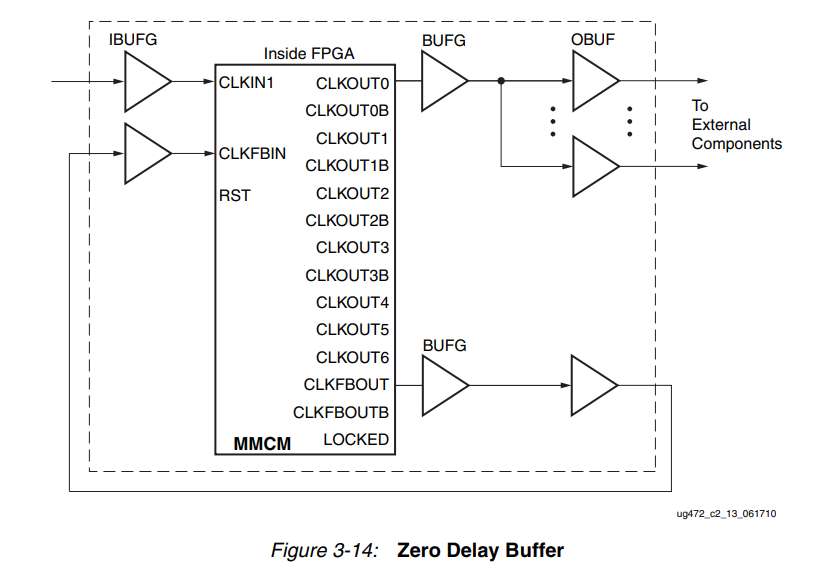

(3)零延迟缓冲器

MMCM 还可用于生成零延迟缓冲器时钟。 零延迟缓冲器对于将单个时钟信号扇出到多个目的地且它们之间的偏斜较低的应用非常有用。 此配置如下图所示。 在这里,反馈信号驱动芯片外,电路板走线反馈旨在将走线与外部组件匹配。 在此配置中,假设时钟沿在 FPGA 的输入和外部组件的输入处对齐。 CLKIN 和 CLKFBIN 的输入时钟缓冲器必须在同一个 bank 中。

这种方法有点像方法1,但是反馈信号与时钟信号都是输出到了FPGA外部,所以不可控因素会变多。在某些情况下,由于外部组件的输入电容和 FPGA 的反馈路径电容之间的负载差异,无法进行精确对齐。 例如,外部组件的输入电容为 1 pF 至 4 pF,而 FPGA 的输入电容约为 8 pF。 信号斜率存在差异,基本上是歪斜的。 设计人员需要意识到这种影响以确保时序。

这种应用适用于单个外部时钟源供给需要保持相位关系的多个数字系统。

4、总结与参考

PLL与MMCM作为FPGA底层内嵌的时钟资源,最大的作用就是实现频率综合、去抖动和去偏斜,本质上就是提供更高质量的时钟

参考资料1:FPGA - 7系列 FPGA内部结构之Clocking -03- 时钟管理模块(CMT)_Vuko-wxh的博客-CSDN博客

参考资料2:xilinx 7系列FPGA理论篇——CMT时钟模块简介_fpga_start的博客-CSDN博客_cmt fpga

PLL与MMCM的基础应用还是非常简单的,但是一些高级应用要用熟练也需要相当多的经验