本文转载自:FPGA技术实战的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

引言:通过属性或者约束可以访问7系列FPGA I/O资源某些特性。本文我们介绍和I/O资源相关的属性和约束:

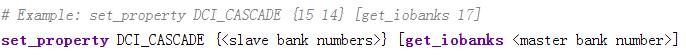

1.DCI_CASCADE约束

DCI_CASECADE约束定义了一个DCI主bank和它对应的从bank。该属性使用以下语法在.XDC文件中进行约束。

图1、DCI_CASCADE约束语法

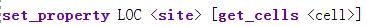

2.位置约束(LOC)

位置约束用来明确使用I/O所处的管脚的位置,位置约束是通过管脚唯一编号来进行的。

图2、LOC约束语法

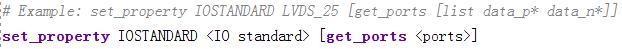

3.IOSTANDARD属性

IOSTANDARD属性用来选择I/O标准电平。

图3、IOSTANDARD属性约束

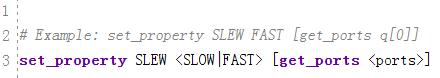

4.输出压摆率属性

输出I/O缓冲器压摆率有SLOW(默认)和FAST两种选择。FAST压摆率可以满足高性能需求,例如高速存储器接口,但是,如果不能恰当设计(端接匹配,传输线阻抗控制和串扰耦合),更高的压摆率输出会导致信号反射或者产生噪声问题。

图4、SLEW属性语法

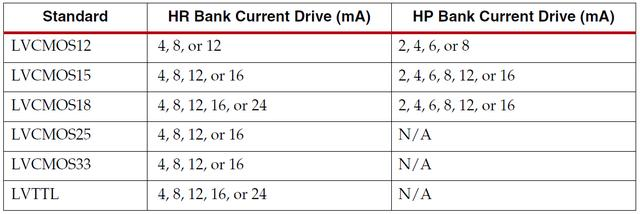

5.输出驱动强度属性

对于LVCMOS和LVTTL输出缓冲器(OBUF,OBUFT和IOBUF),可以通过DRIVE属性设置驱动电流强度。

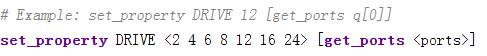

图5、DRIVE属性允许设置值

图6、输出电流强度约束

6.PULLUP/PULLDOWN/KEEPER属性

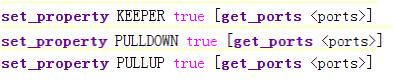

输入缓冲器(IBUF)、三态输出(OBUFT)和双向缓冲器(IOBUF)有弱上拉,弱下拉或者"keeper"电路。

图7、PULLUP/PULLDOWN/KEEPER属性

7.差分端接属性

差分端接属性(DIFF_TERM)用于差分输入I/O,用于打开或关闭芯片内置100Ω差分端接电阻。片上输入端接电阻比芯片外部分立电阻端接更能改善信号完整性,因为片内端接电阻在接收器侧不存在stub(由PCB设计引起,可以通过背部钻孔消除,会带来PCB制造成本增加)。该属性应用于以下I/O标准:

图8、DIFF_TERM属性约束语法

当使用DIFF_TERM属性是,必须对LVDS或者其他2.5V电平标准I/O bank提供恰当电压,并且该属性只用于输入差分I/O。

8.内部VREF

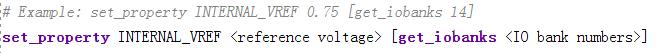

7系列FPGA的VREF电压可以由芯片内部产生或者由外部电源供电,使用芯片内部产生VREF电压可以消除外部电源供电。当VREF管脚不作为电源管脚使用或者使用内部参考电源(INTERNAL_VREF)时,它可以作为普通I/O使用。内部产生的VREF来自VCCAUX电源,每个bank有一个单独的VREF电源层。

图9、内部VREF属性约束

芯片内部参考电源有以下几种选择:

9.VCCAUX_IO约束

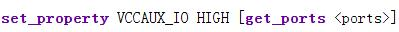

VCCAUX_IO管脚可以设置为1.8V或者2.0V电压,当设置为2.0V电平时,需要对VCCAUX_IO添加约束,默认为1.8V电平。

图10、VCCAUX_IO属性约束

在一个bank中,如果VCCAUX_IO管脚供电为2.0V,则在该bank至少一个I/O net管脚或者原句将VCCAUX_IO属性约束为HIGH,其他所有I/O net或者原句可以约束为HIGH或者DONTCARE。

总结

■ 这些属性及约束我们在进行FPGA软件设计时会用到,有些约束需要配合硬件进行,比如参考电压VREF的设计等。熟练应用这些约束对于我们更好的发挥FPGA器件性能具有意义。

■ 这些属性及约束的语法我们可以在Vivado IDE “Language Templates”里找到。