本文转载自:十年老鸟的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

器件:Xilinx zynq zu6cg

版本:vivado2019.2

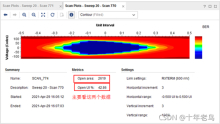

实现:12.16512G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为122.88MHz

目的:记录从仿真到上板调试的过程,方便回忆

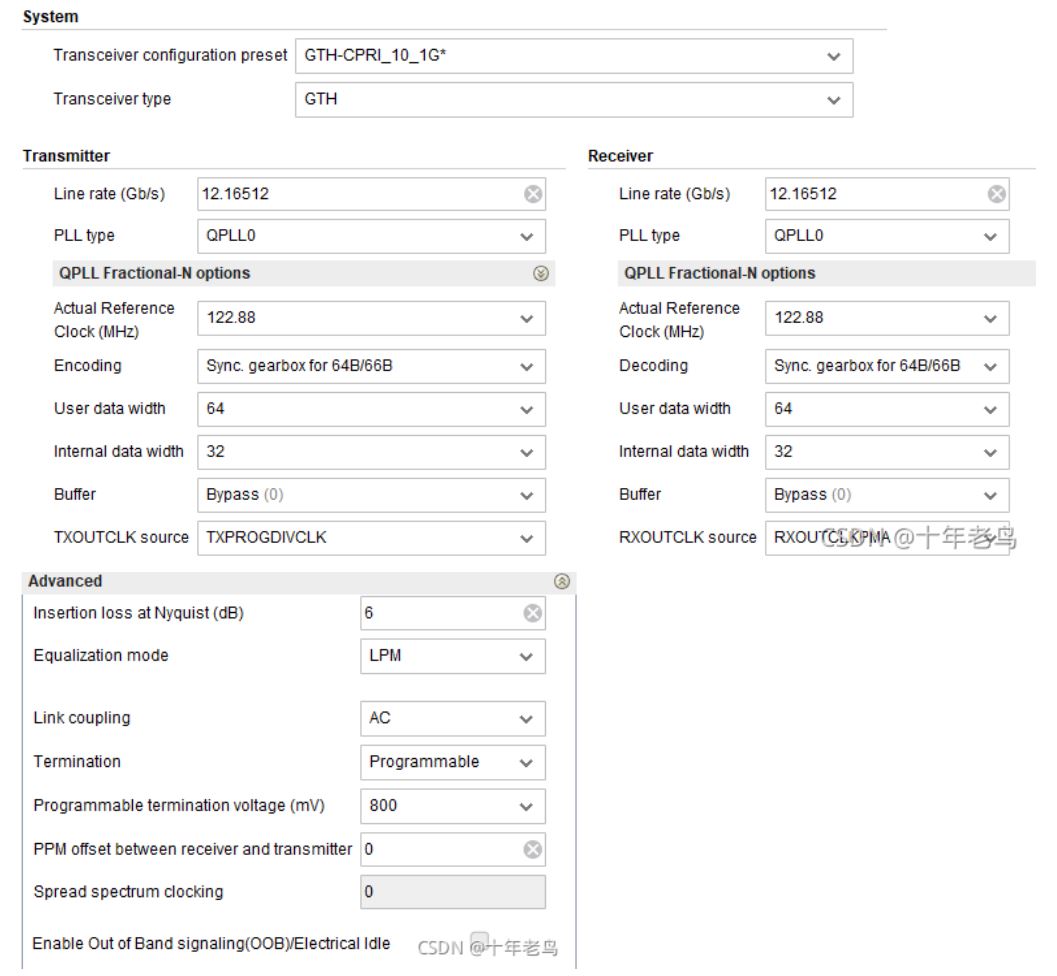

IP核的详细设置

第一个选项卡 basic

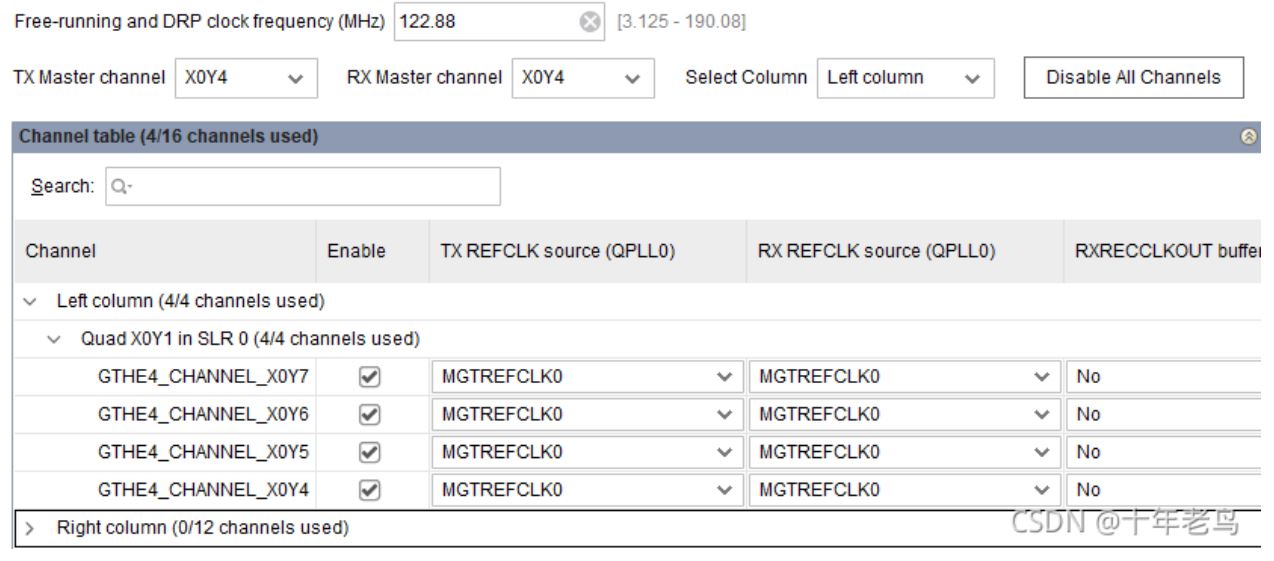

第二个选项卡 Physical Resources

第三个选项卡 Optional Features

没有要设置的

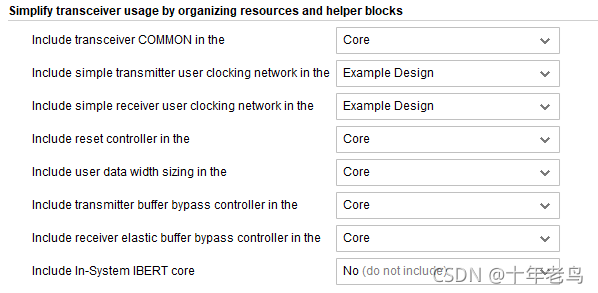

第四个选项卡 Structural Options

后面的可选输出端口绝大部分不用勾选,可以勾选回环这种,方便测试

最后,生成IP核后,鼠标放到IP核右键,点击open IP example design,生成了一个example的工程

IPexample的使用

IPexample改动和之前10G的思想类似,只不过zu6cg和zynq 7035的serdes模块有一些差异,因此有些改的地方会有不同。Zu6cg的serdes example不自带加解扰模块,这个还需要自己加。

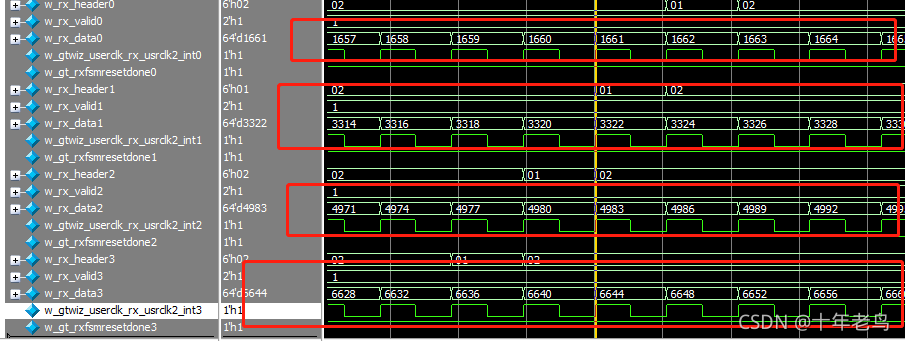

输入一个累加数,将sedes输出管脚直接连入输入管脚(仿真的时候),看接收的数据是否也是累加数。

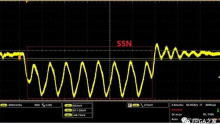

该工程可以直接用于上板调试,直接用光口1和光口2进行光纤对接,通过ILA抓取接收的数据,也是累加数,则是正常。

该模块可直接用于实际应用中。

附件

下载地址:

SERDES_12G

SERDES_12G.rar中

gtwizard_0_ex_yuanshi为 IP example直接生成的工程,

gtwizard_0_ex_xiugai 为在上面基础上修改的工程。

在gtwizard_0_ex_xiugai文件夹中 找到啊 tb.tcl,修改tcl中的文件路径后,直接可以modelsim运行(modelsim要提前配置好库文件)

运行结果如下图所示,即成功