本文转载自: Spinal FPGA微信公众号

本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。自此仿真设计一体化不是问题~

环境依赖

SpinalHDL 1.7.1 (如果使用 1.7.0 版本,需要每次在 VCS 运行前导入 synopsys_sim.setup 文件到仿真目录)

Xilinx Vivado 2021.2

Synopsys vcs-mx_O-2018.09-SP2

Synopsys Verdi _O-2018.09-SP2

GCC/GXX 4.8.5

IDEA 2021

使用 VCS 预编译 Xilinx 官方 IP

首先将默认的 gcc/g++ 切换到 4.8.5 版本

打开 vivado,在 Tools → Compile Simulation Libraries,选择仿真器 VCS,其他按需选择。

选择 预编译库保存路径 以及 VCS 可执行路径。

由于一开始选择了默认版本gcc/g++,这里直接使用默认执行路径。

下面是笔者的配置图:

Click Compile 等待完成…(3 min的样子)

结束后会有部分编译失败,这是因为 System C 的环境没有配置,但由于该部分组件笔者不会使用到,便忽略了。

此时,前面选择的预编译库保存路径下会出现synopsys_sim.setup 配置文件,用于 vcs 启动前自动加载预编译库。

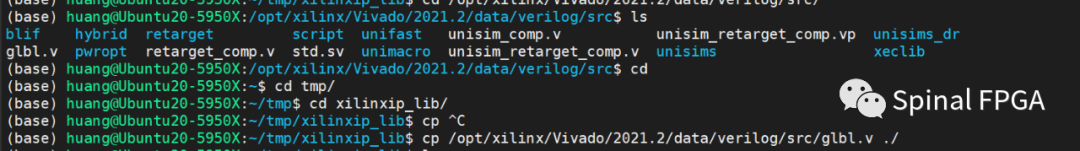

同时可以将 ${vivado_install_path}/${verison}/data/verilog/src/glbl.v 复制到预编译库的文件夹下,方便后续使用

配置 Idea

使用 IDEA 配置 SpinalHDL 运行环境。

GitHub - SpinalHDL/SpinalTemplateSbt: A basic SpinalHDL project

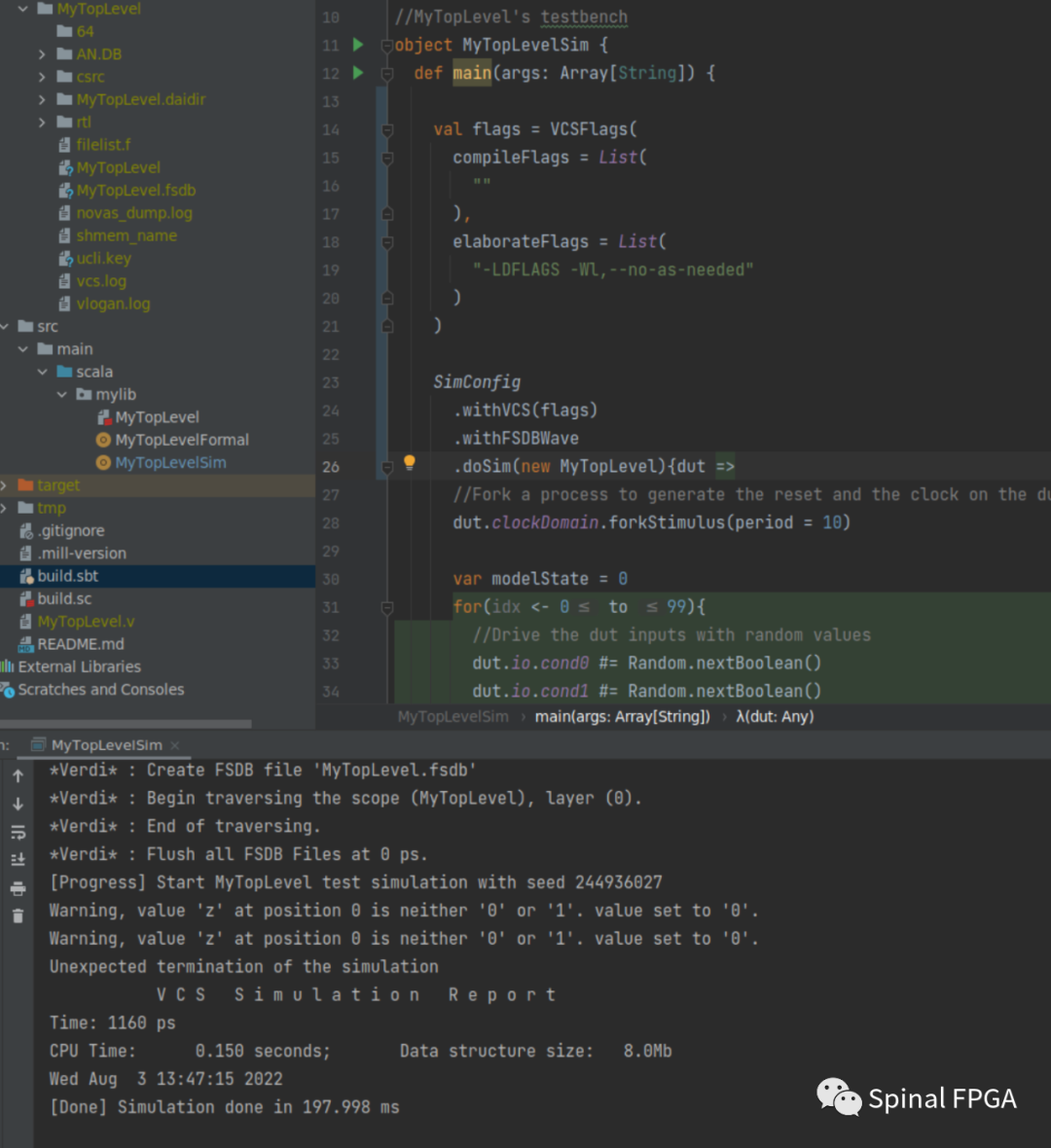

以 Template 工程为例,配置 SpinalHDL 调用 VCS 仿真。

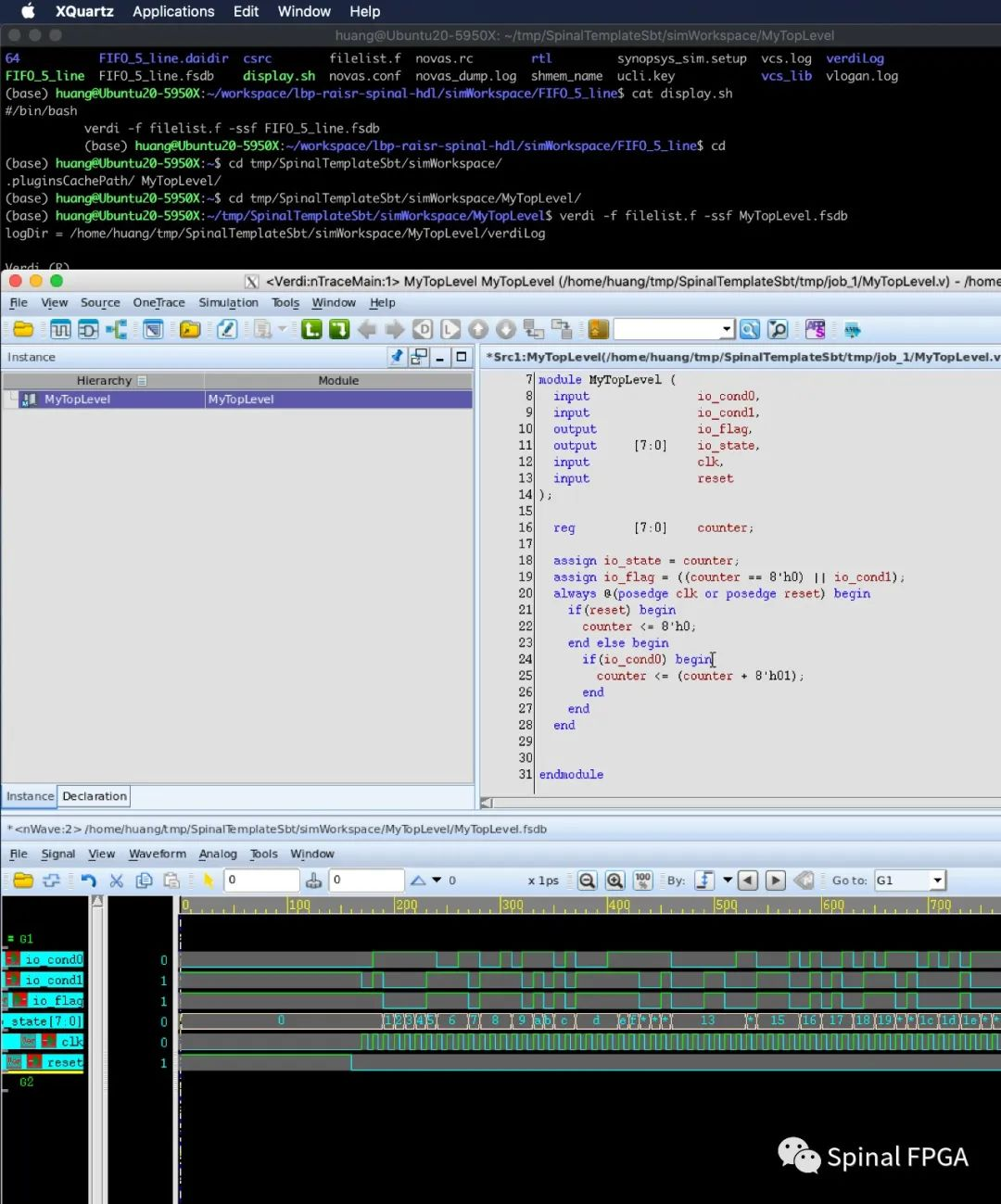

在命令行中用 verdi 打开波形,正常打开则 VCS 仿真环境已正常运行。

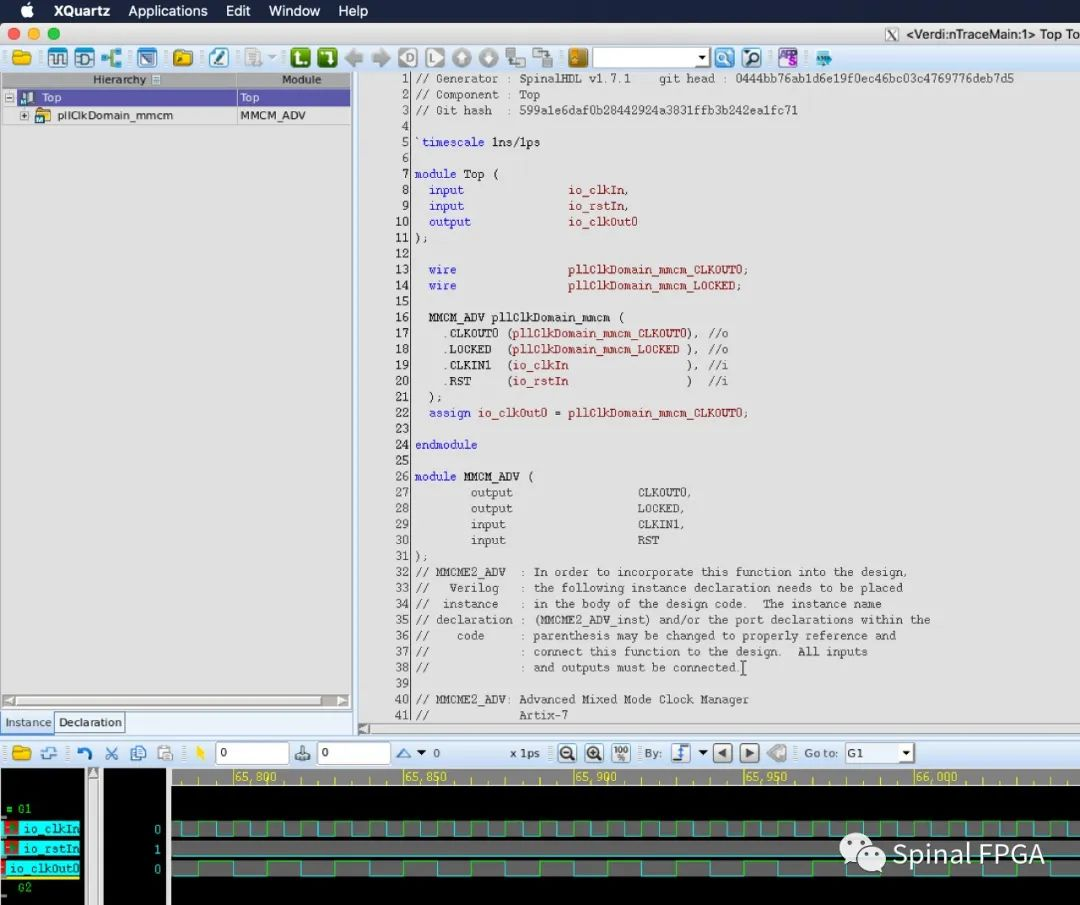

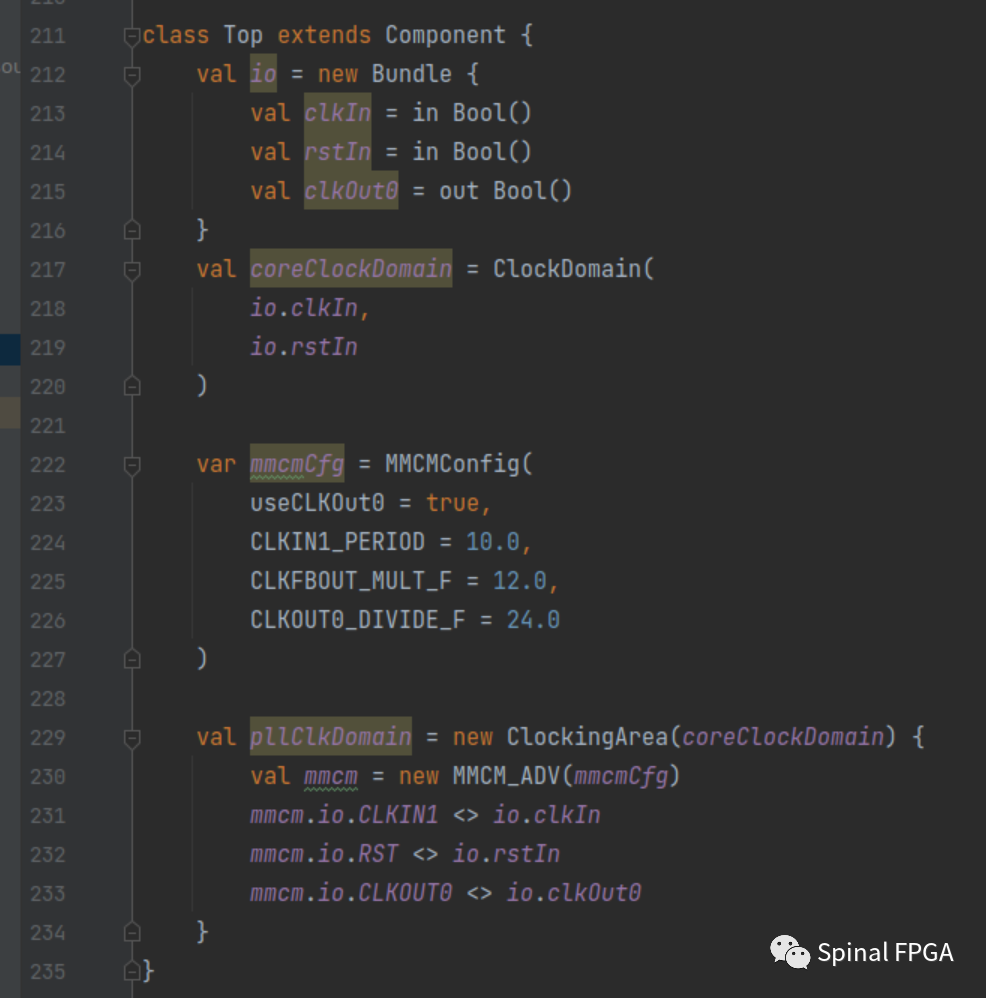

以使用 xilinx PLL 为例,为了减少使用 vivado 编译 ip 后导入(每次不同的设置都需要重新配置),笔者直接使用 XPM 模板进行例化。(可以在 xilinx xpm 手册或者是 Tools → Language Templates 中找到)。需要使用 BlackBox 对 XPM 模板进行封装

封装后尝试一下例化该 PLL 做一个 二分频。

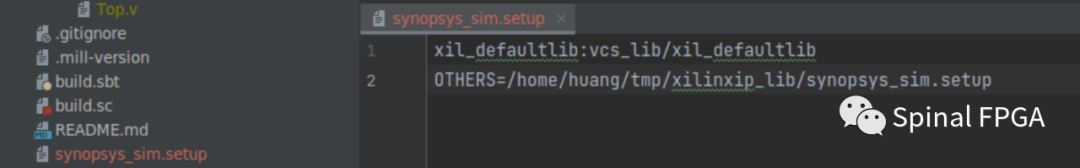

在该工程根目录下,创建名为 synopsys_sim.stup 一个指向预编译库的文件。里面填写预编译库对应生成的 setup 文件的目录。下面是笔者的 synopsys_sim.setup 文件。

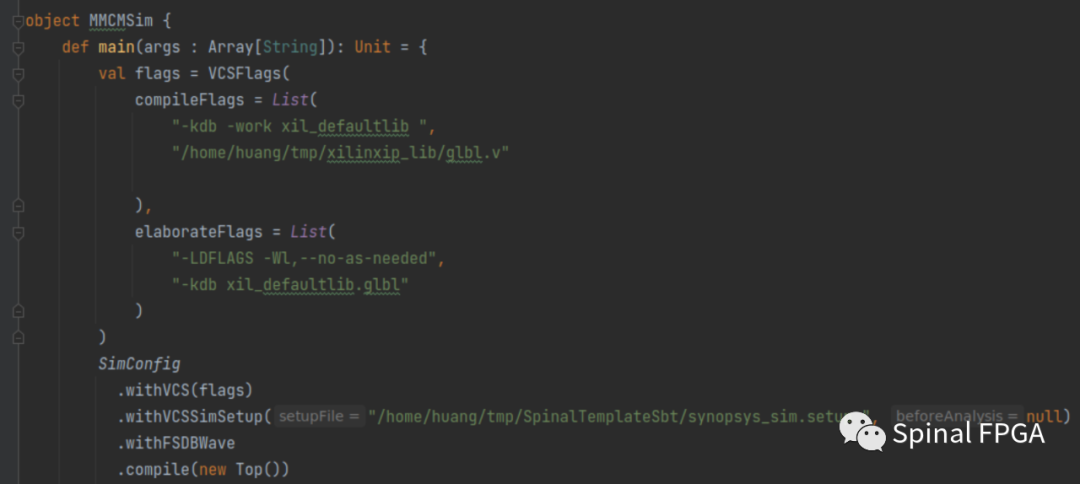

SpinalHDL 调用 VCS 仿真 xilinx ip 前环境,需要将文件复制到当前仿真目录(1.7.1不需要手动拷贝,1.7.0需要手动,注意的是SpinalHDL每次仿真都会清空仿目录)。需要注意是:仿真 xilinx ip 需要加入 xilinx 的全局复位控制(上次没加,仿真 DSP 被坑了好久…)

此时配置完成了,试一下仿真吧~