本文转载自:明德扬FPGA科教微信公众号

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制和读写时序的情况下,也能通过MIG IP控制器读写DDR存储器。

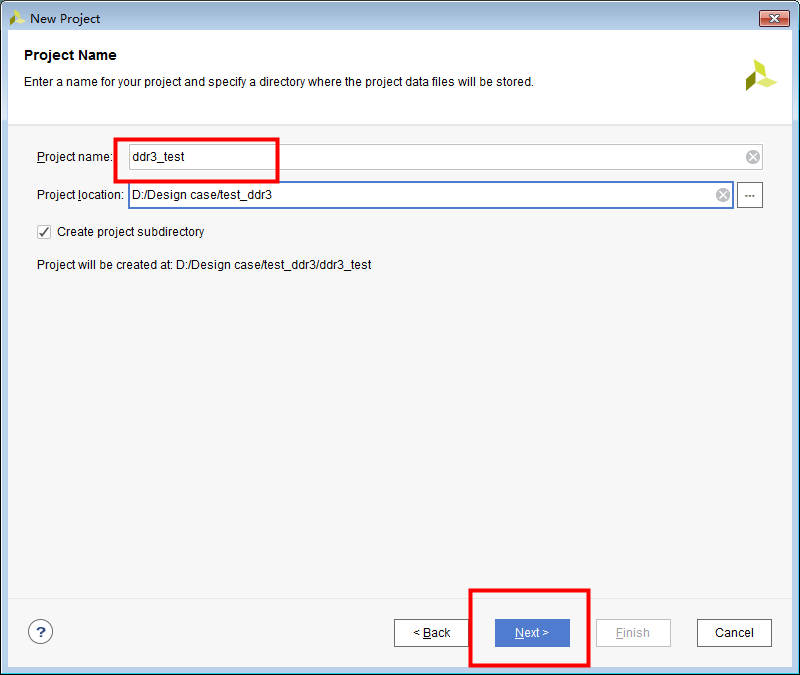

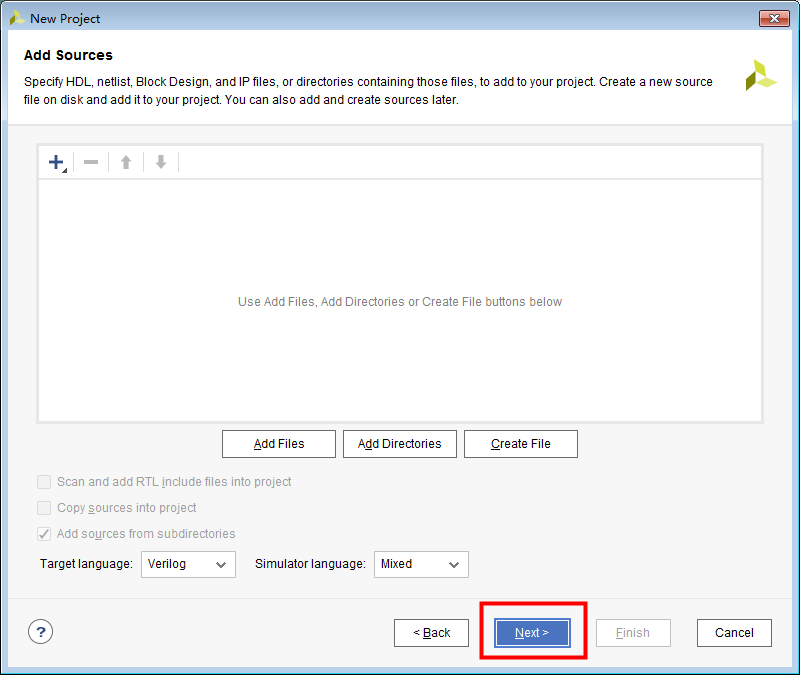

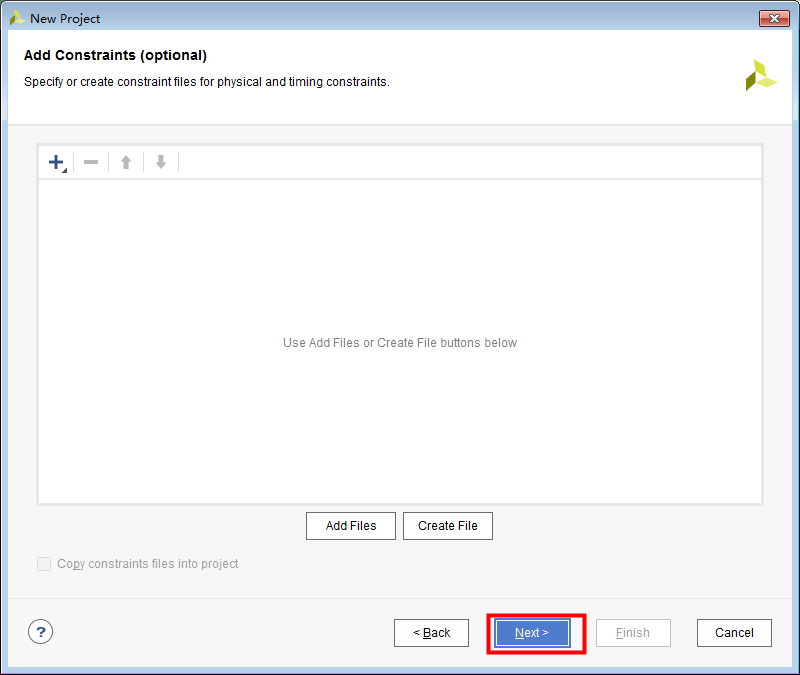

一、新建工程

在Vivado环境里新建一个项目,可取名为 ddr3_test。

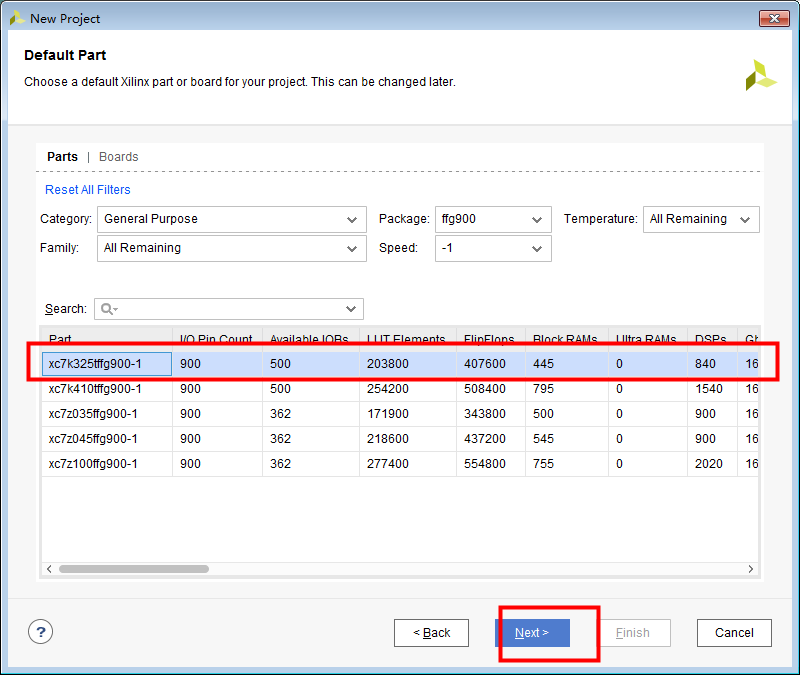

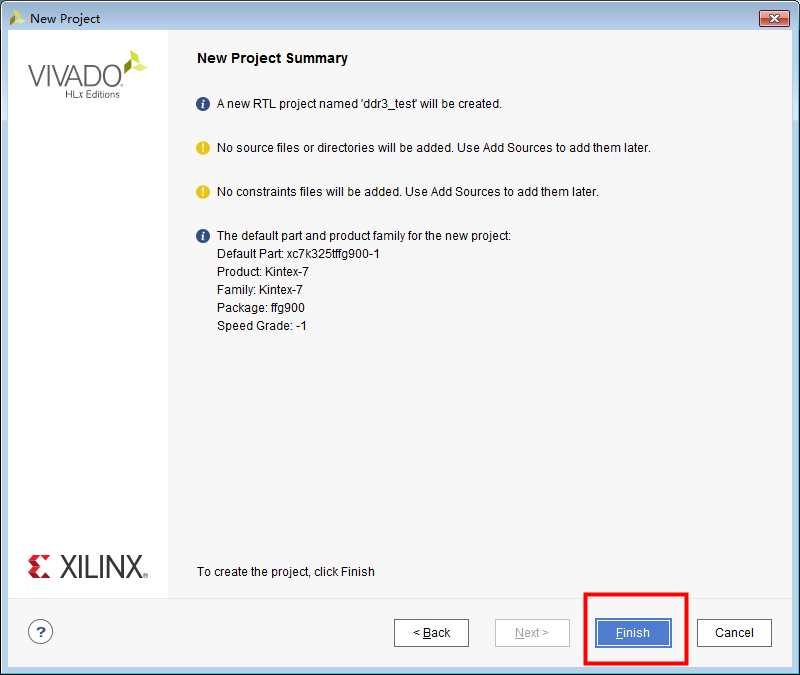

这里的芯片型号各位可以根据需要选择,我们选择的是:xc7k325tffg900-1(如下图所示):

点击“Finish”结束工程的建立:

二、进入IP核配置界面

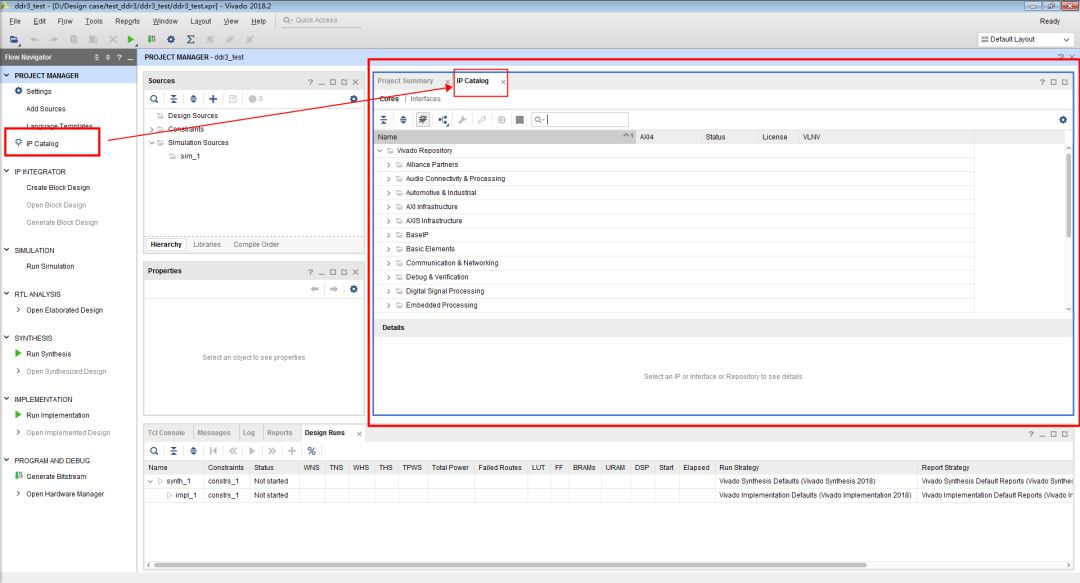

在Vivado左边界面“Project Manager”选项下,点击“IP Catalog”,进入如下图所示界面。

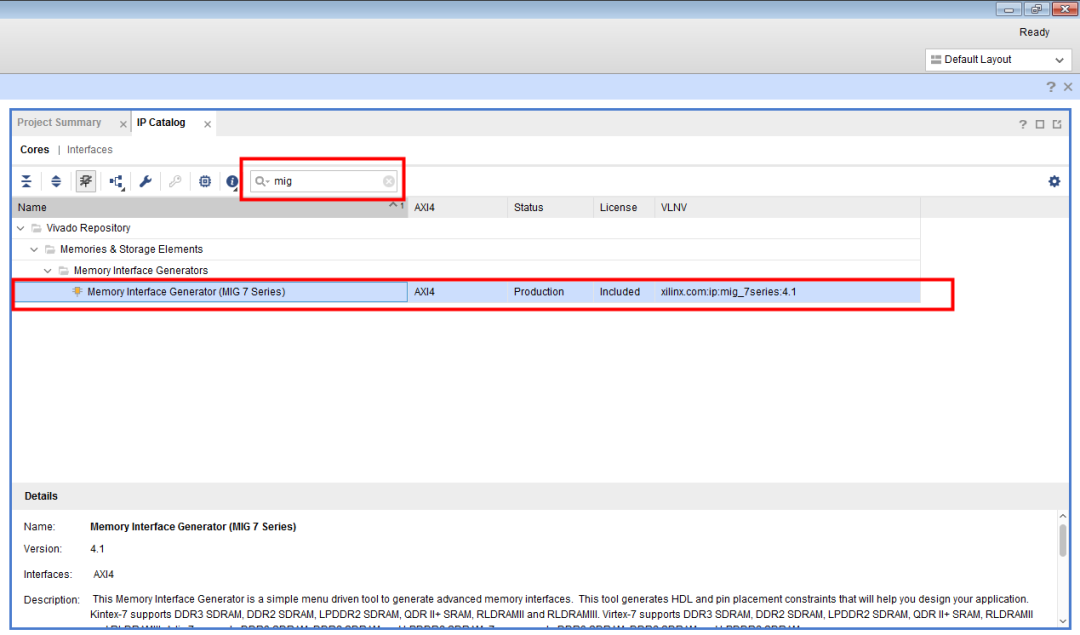

可以在搜索栏输入“MIG” 快速查找, 双击“Memory Interface Generate (MIG 7 Series)”进入DDR IP核配置界面(如下图所示)。

三、IP核配置

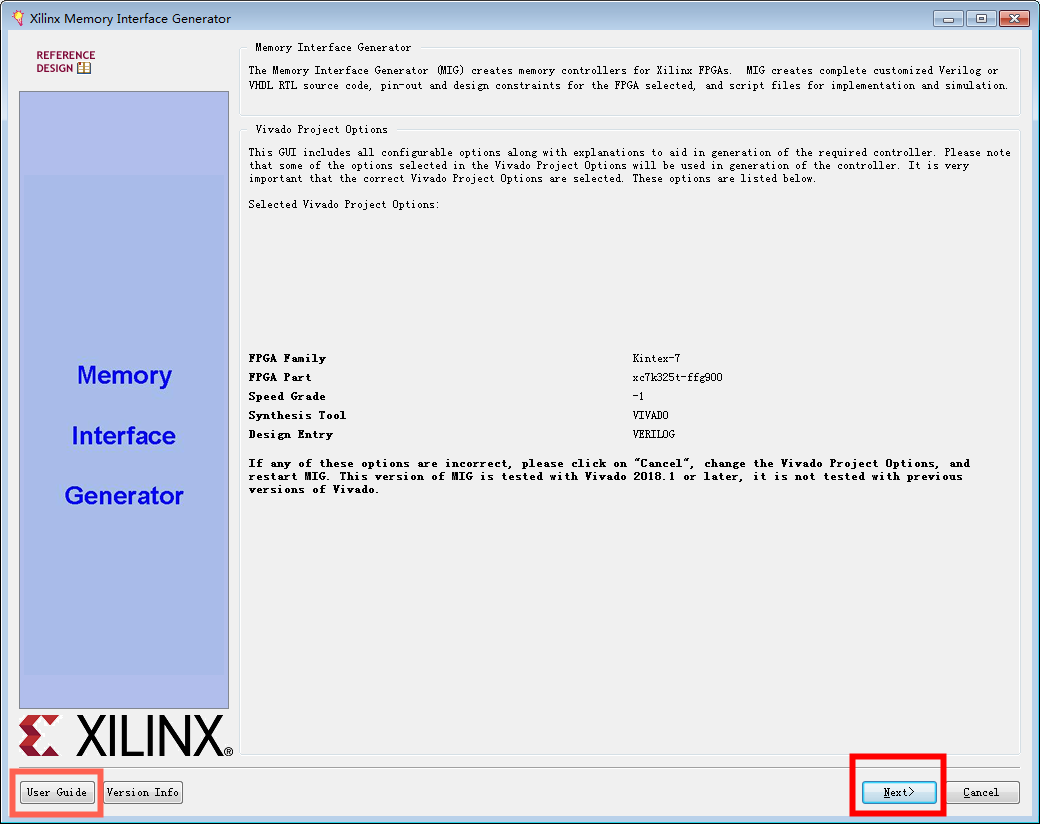

点击“Next”(如果想了解更多关于MIG的信息,可以点击左下角的“User Guide”来打开Xilinx的相关文档)。

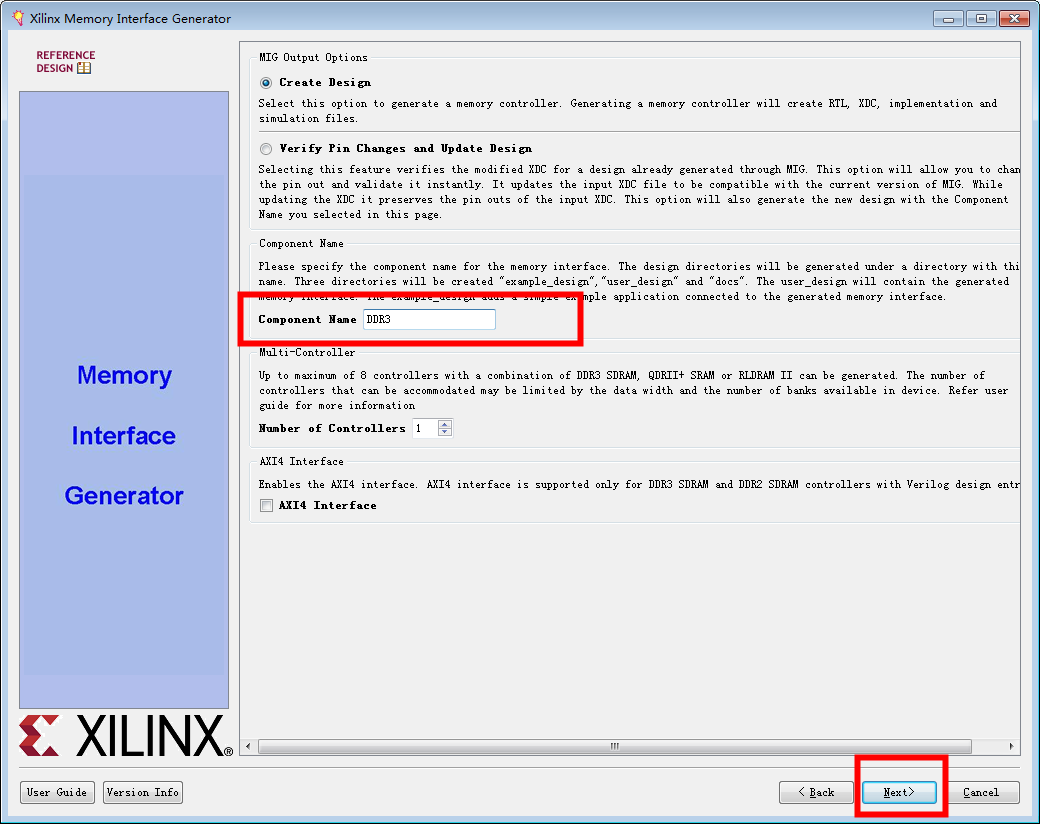

修改“Component Name”为“DDR3”,点击“Next”(如下图所示)。

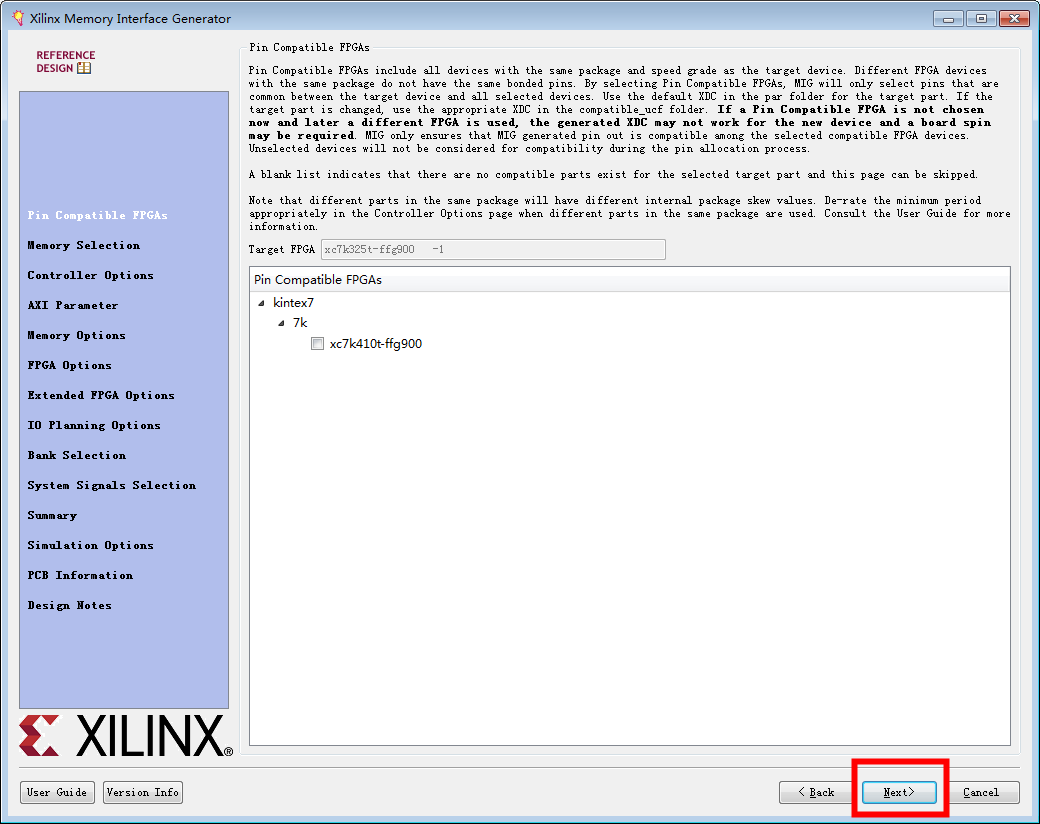

这里可以选择兼容的芯片,但我们不需要,直接点击“Next”(如下图所示)。

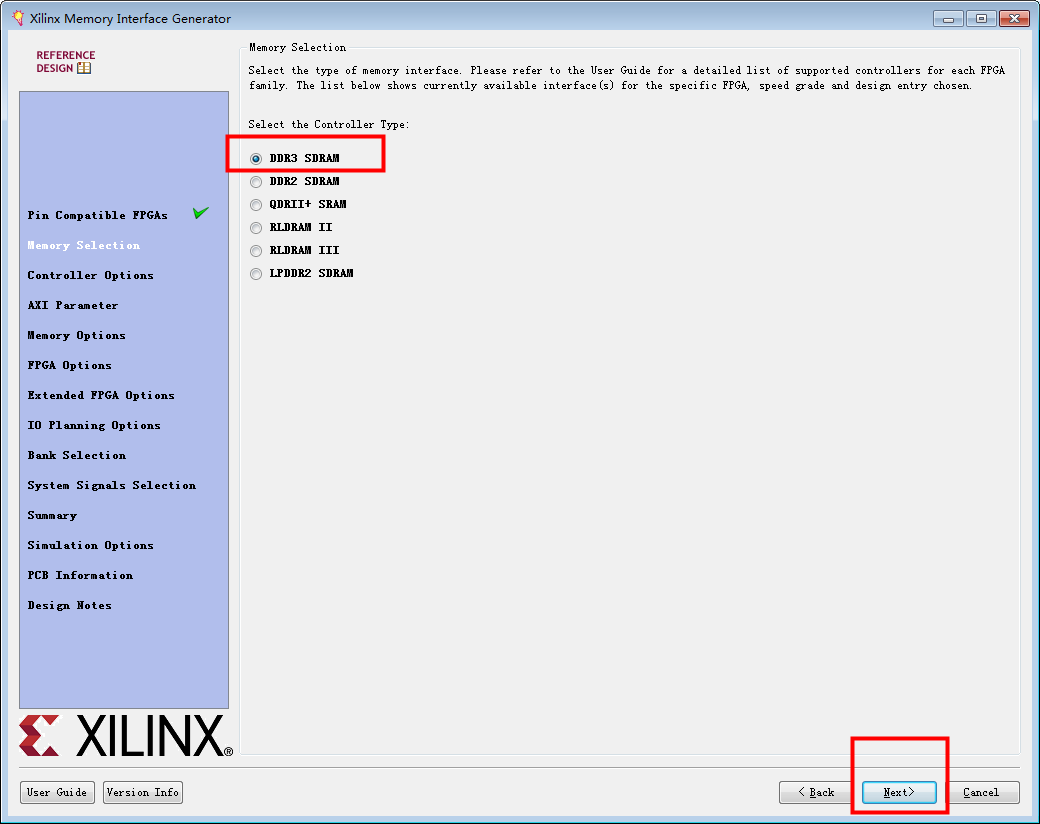

直接选择默认的“DDR3 SDRAM”,然后点击“Next”(如下图所示)。

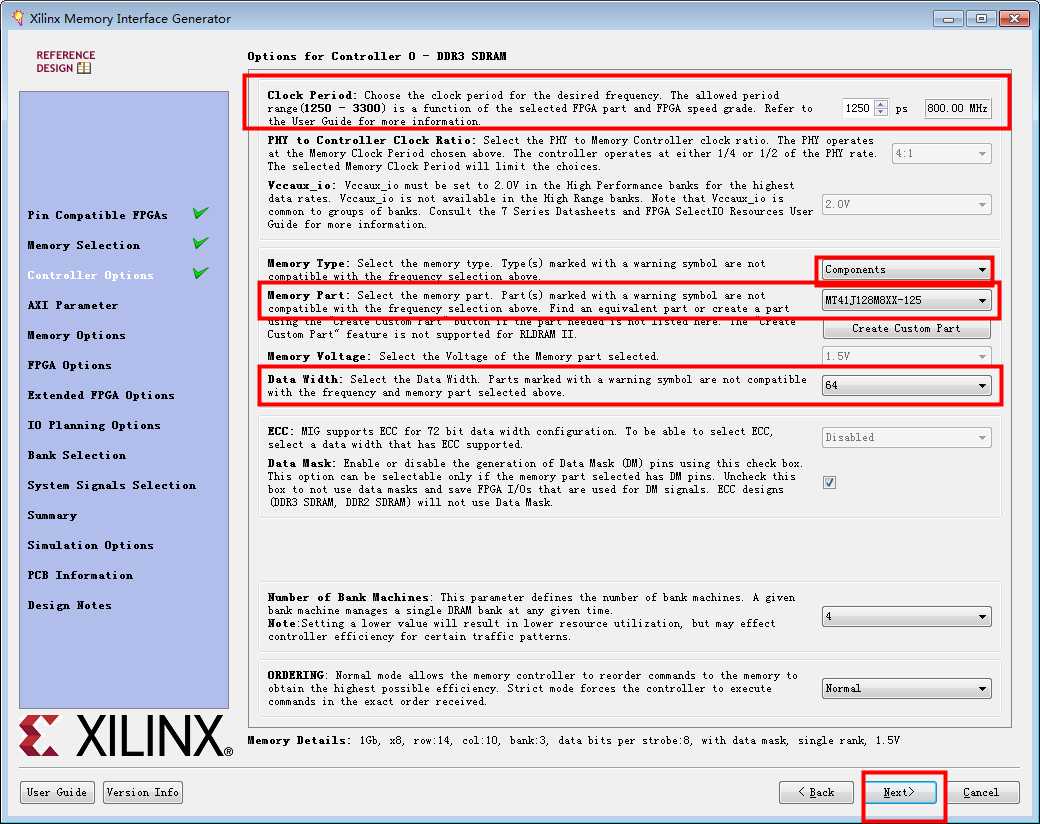

在“Memory Part”选项中, 选择开发板上的型号“MT41J256m16XX-125”,数据宽度“Data Width”选择“64”位;最后“Next”(如下图所示①)。

图①:DDR3 MT41J256m16XX-125设置

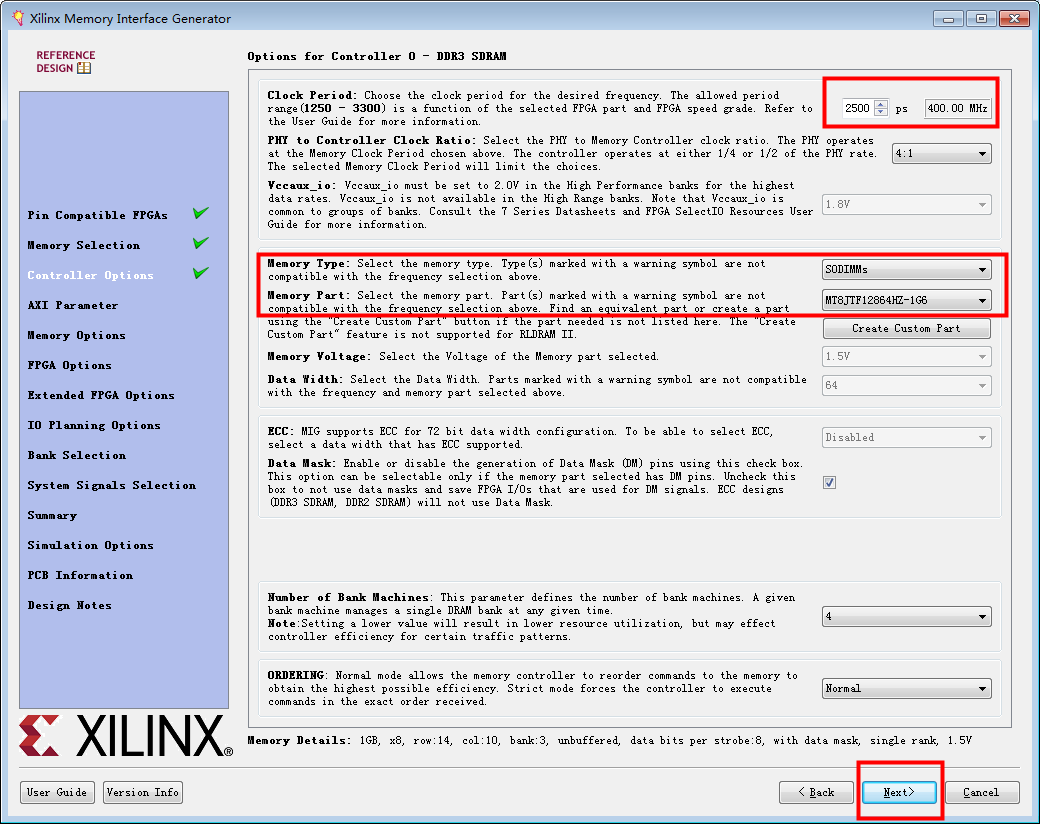

或者在“Memory Type”选项下, 选择“SODIMMs”;在“Memory Part”选项下镁光内存条型号这里可选为“MT8JTF25664HZ-1G6”;在“Clock Period”设置参数为“2500ps”、“400.00MHz”(如下图所示②);最后“Next”。

图②:型号为 MT8JTF25664HZ-1G6的镁光内存条设置

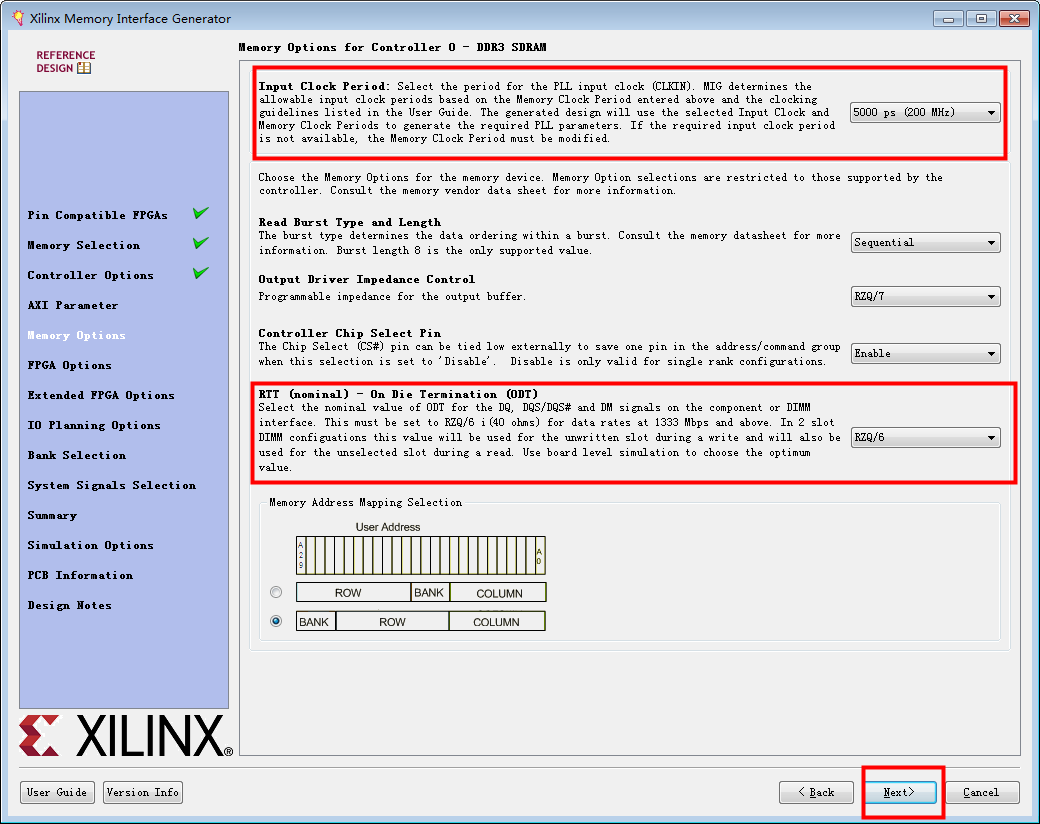

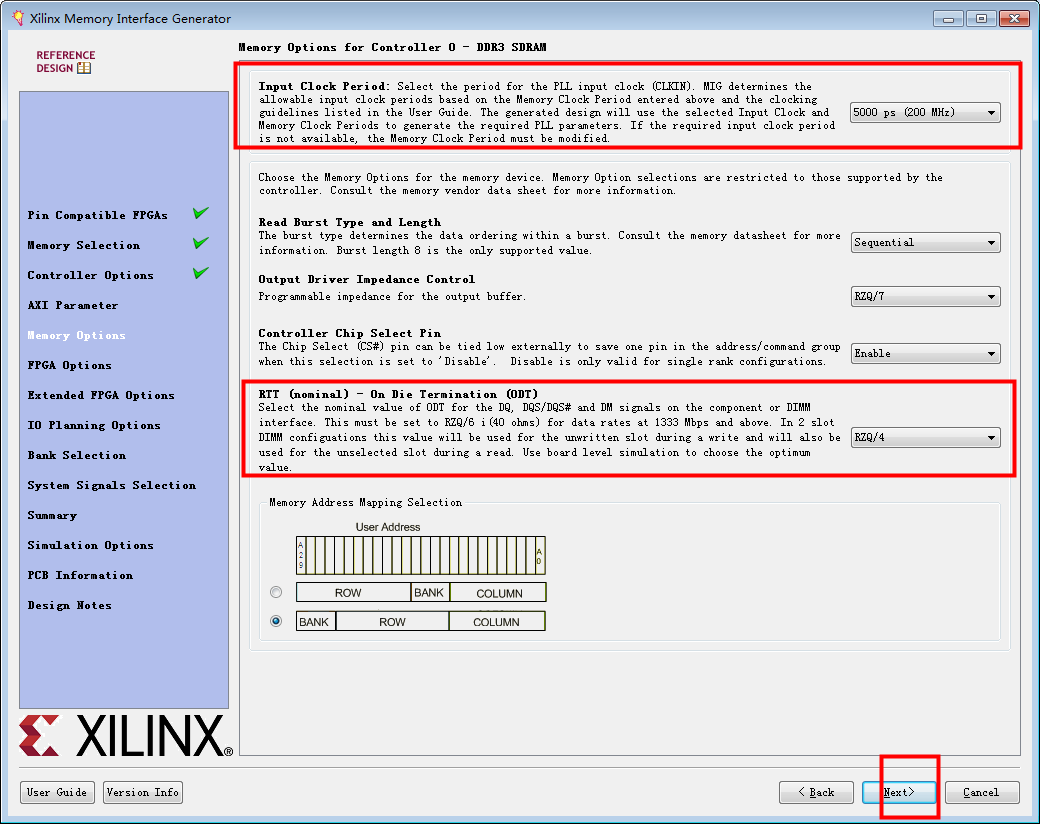

选择PLL输入时钟的频率“Input Clock Period”为“200MHz”(这个时钟需要与开发板上的时钟频率一致);“RTT(nominal)- On Die Termination(ODT)”选项下的 板载DDR3RTT选择“RZQ/6”(MT8JTF25664HZ-1G4选择默认“RZQ/4”);其他设置输出阻抗值和内部的ODT内部上拉电阻值来改善DDR3的信号完整性,一般不需要修改(如下图③/④所示);最后点击“Next”。

图③:DDR3 MT41J256m16XX-125设置

图④:型号为 MT8JTF25664HZ-1G6的镁光内存条设置

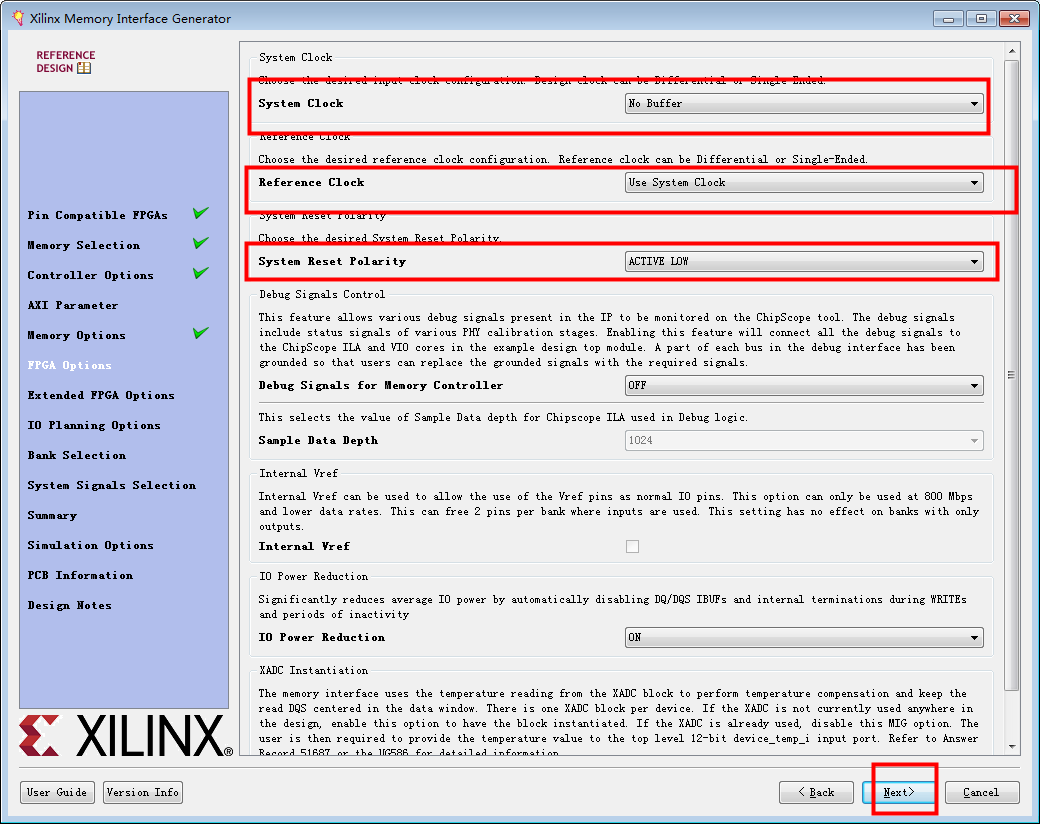

在“System Clock”选项下选择差分“No Buffer”;在“Reference Clock”选项中,因为开发板上没有提供单独的DDR参考时钟,所以选择“Use System Clock”;在“System Reset Polarity”选项下选择“ACTIVE LOW”,其它选项保留默认配置(如下图所示)。

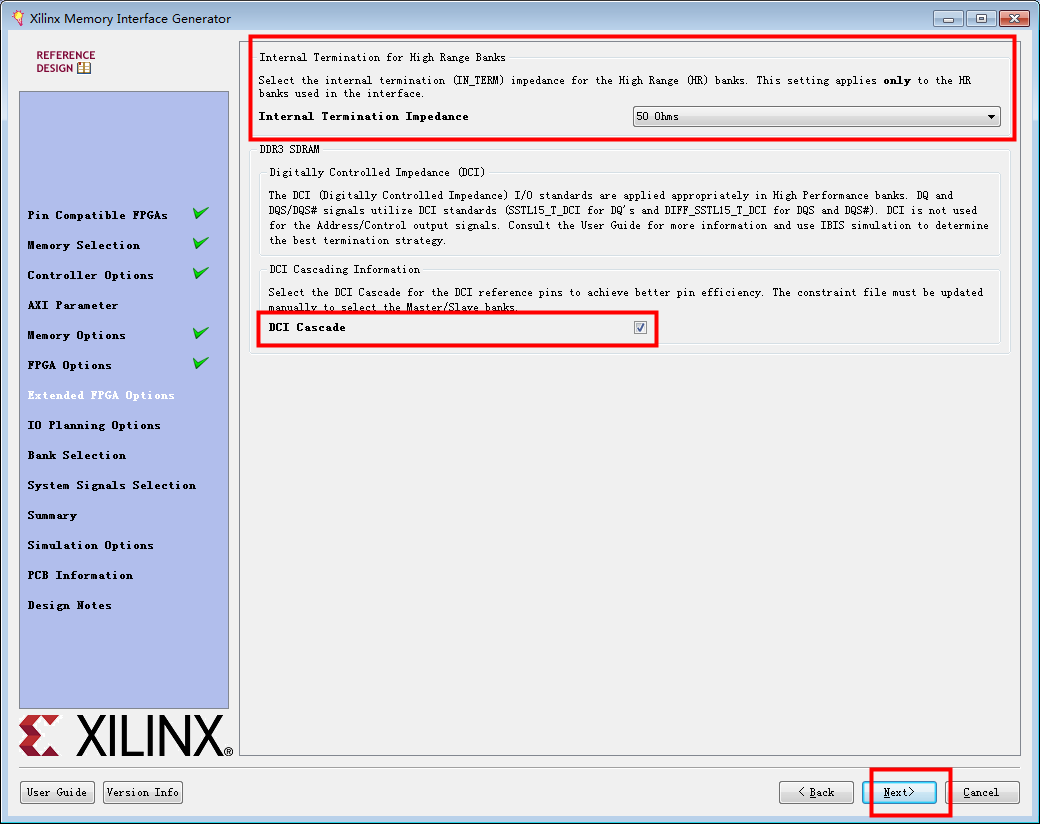

在“Internal Termination ImPedance”选项中High Range Banks 的内部端接阻抗,这里选择默认的“50 ohms”;在“DCI Cascade”选项下“勾选”(如果是镁光内存条MT8JTF25664HZ-1G6则不勾选)(如下图所示)。

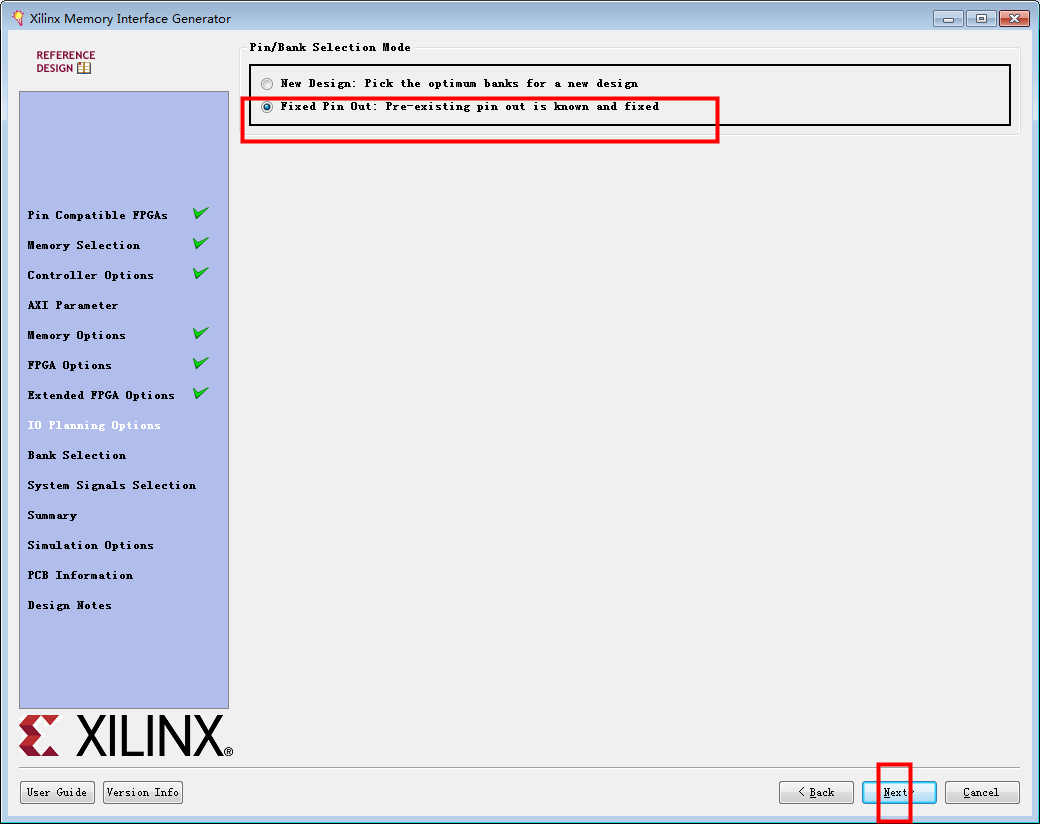

点击选择第二项,设定一下DDR的管脚,然后点击“Next”(如下图所示)。

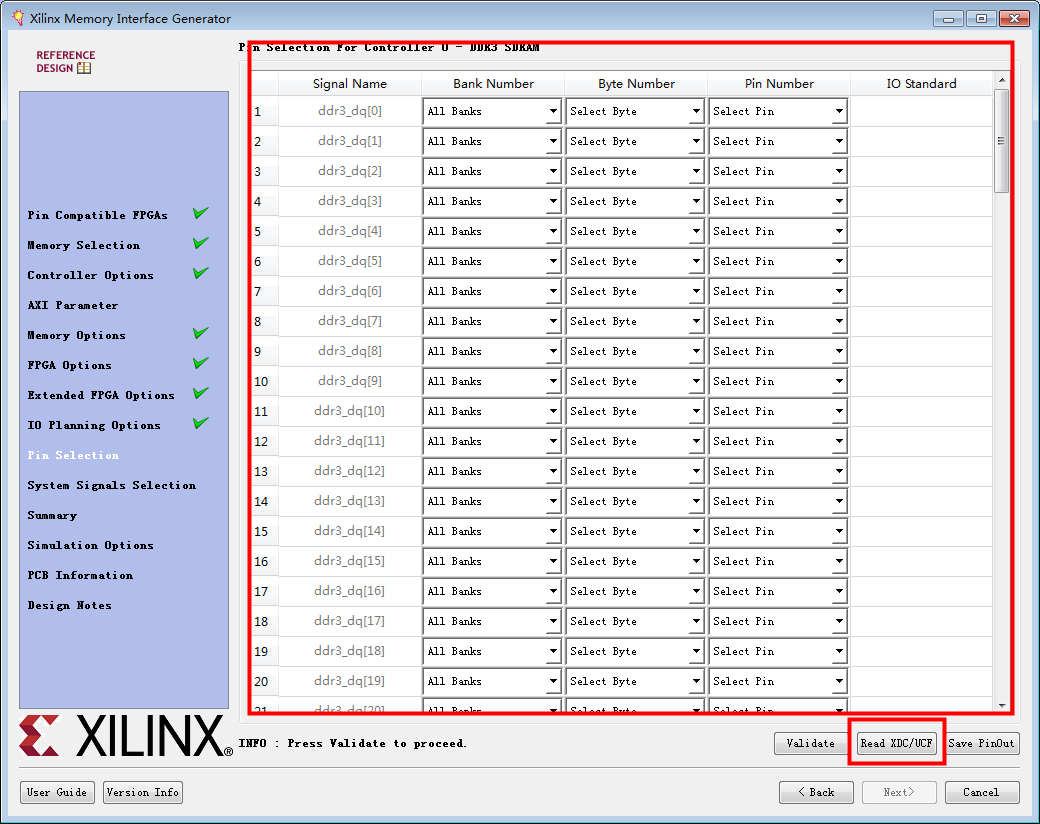

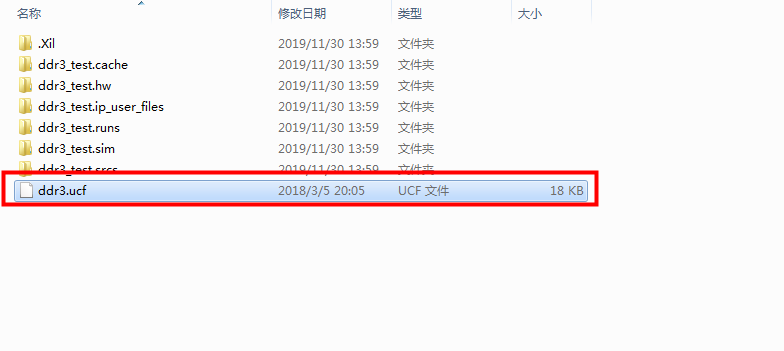

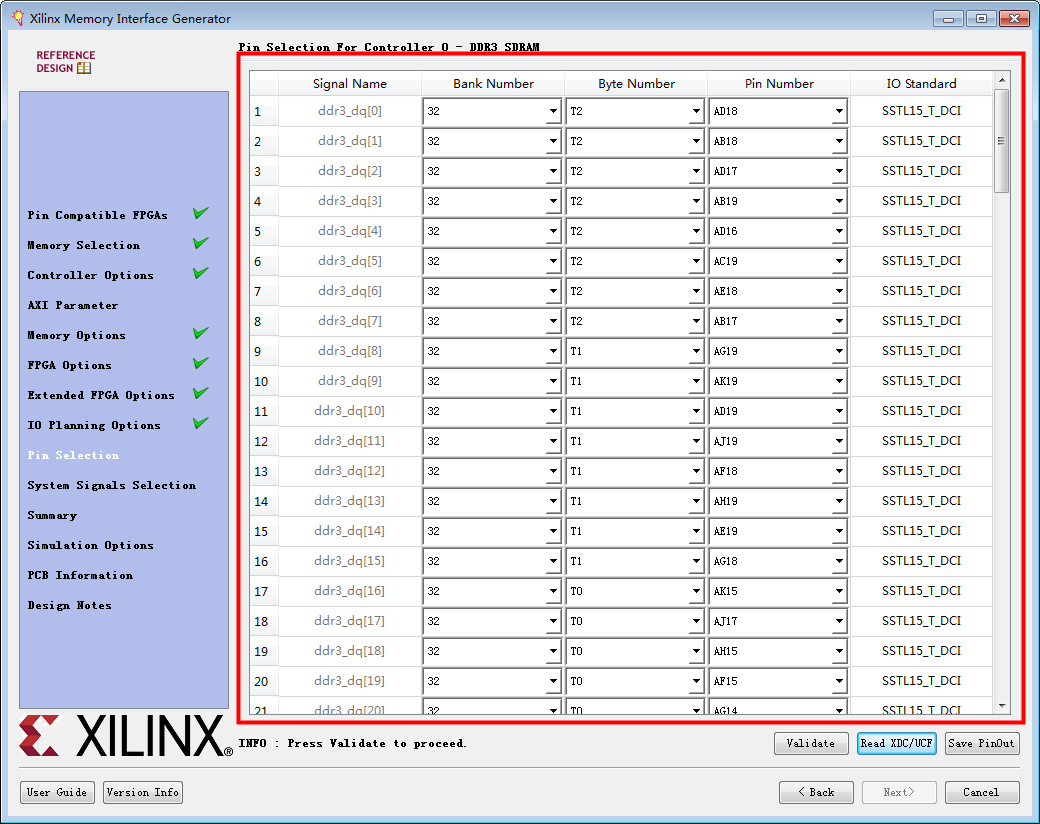

在以下界面设置DDR3的数据、地址和控制信号的FPGA管脚分配和IO电平。但这个手工分配比较费劲,此时可以点击“Read XDC/UCF”直接导入管脚分配文件(.ucf文件)。(如下图所示)

在本例程中我们已经为大家准备好了一个ddr3.ucf文件,只要直接导入这个.ucf文件就可以完成 ddr3 的管脚分配(内存条 MT8JTF25664HZ-1G4,则选择 dimm.ucf 文件)。

导入完成如下:

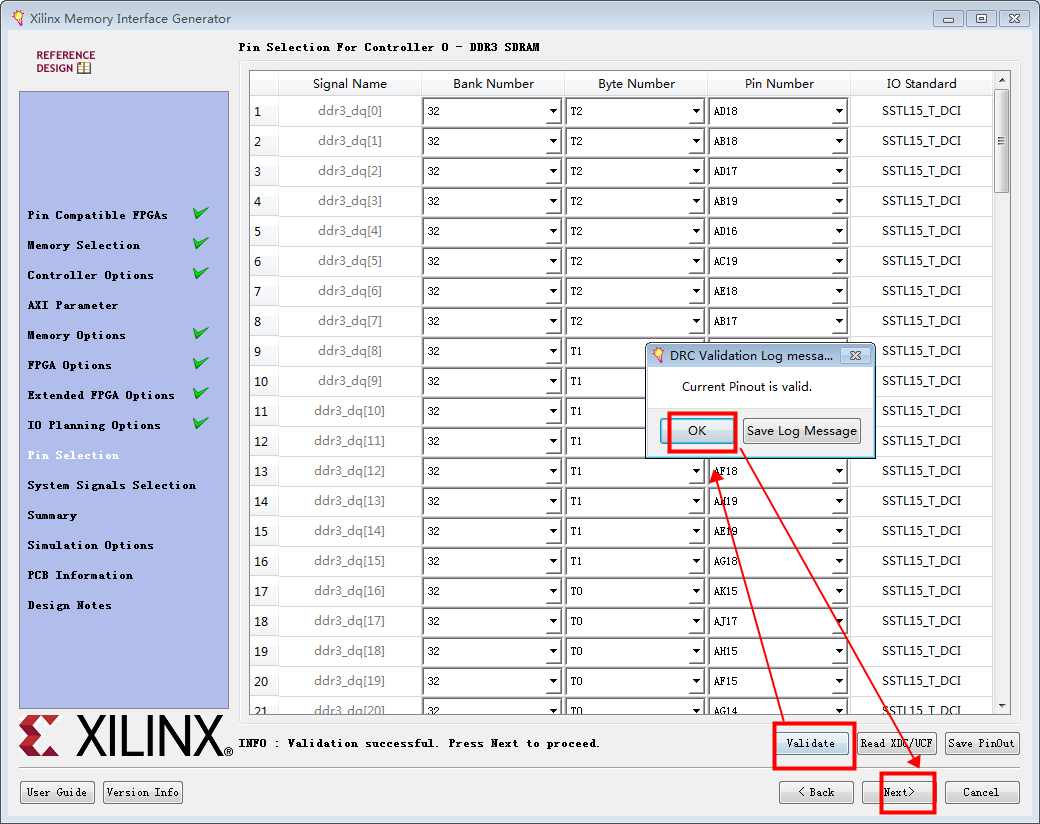

接着再点击“Validate”验证一下,通过后点击“Next”(如下图所示)

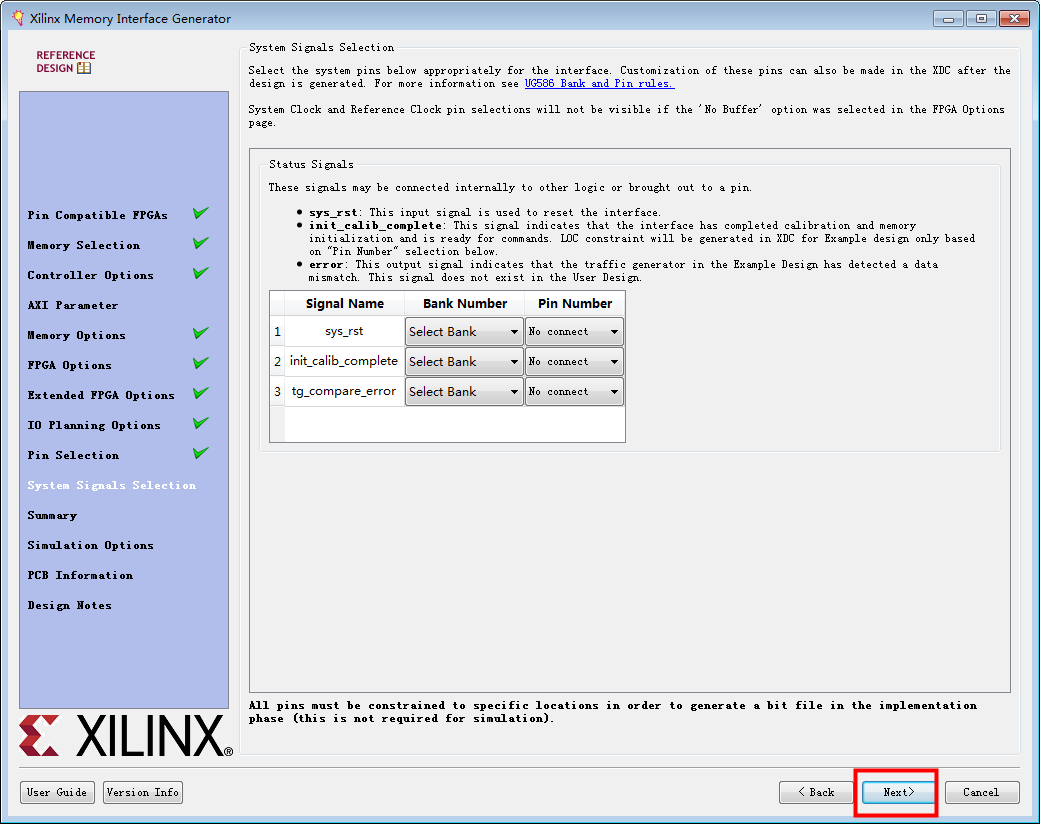

这里保留默认设置,直接点击“Next”。

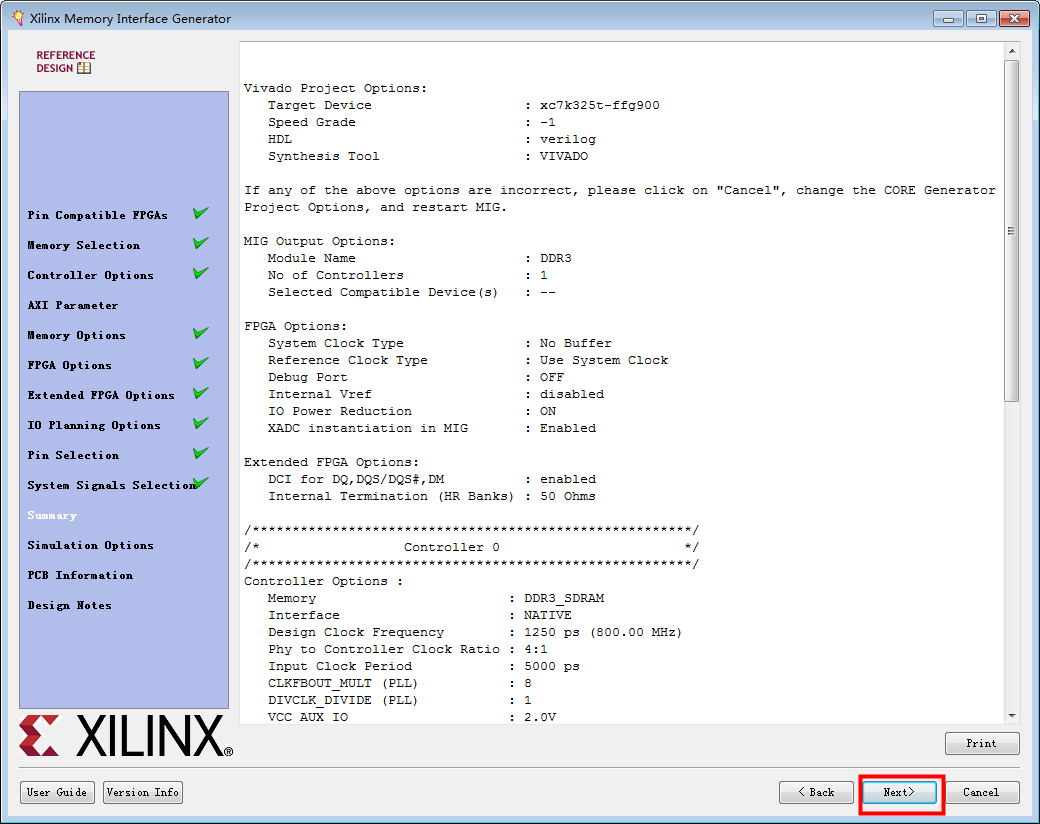

接下来显示的是DDR3 IP核配置的整体情况,检查看看有没有什么问题,没有问题就点击“Next”(如下图所示)。

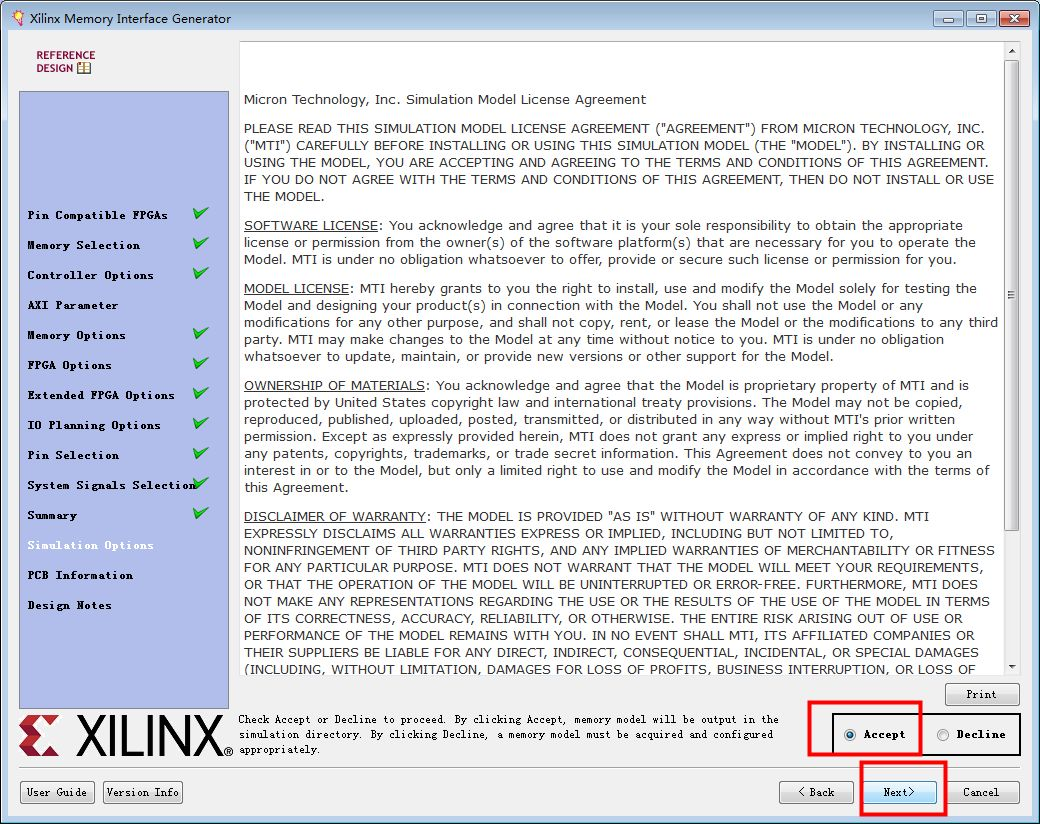

选择“Accept”,点击“Next”,“Next”。

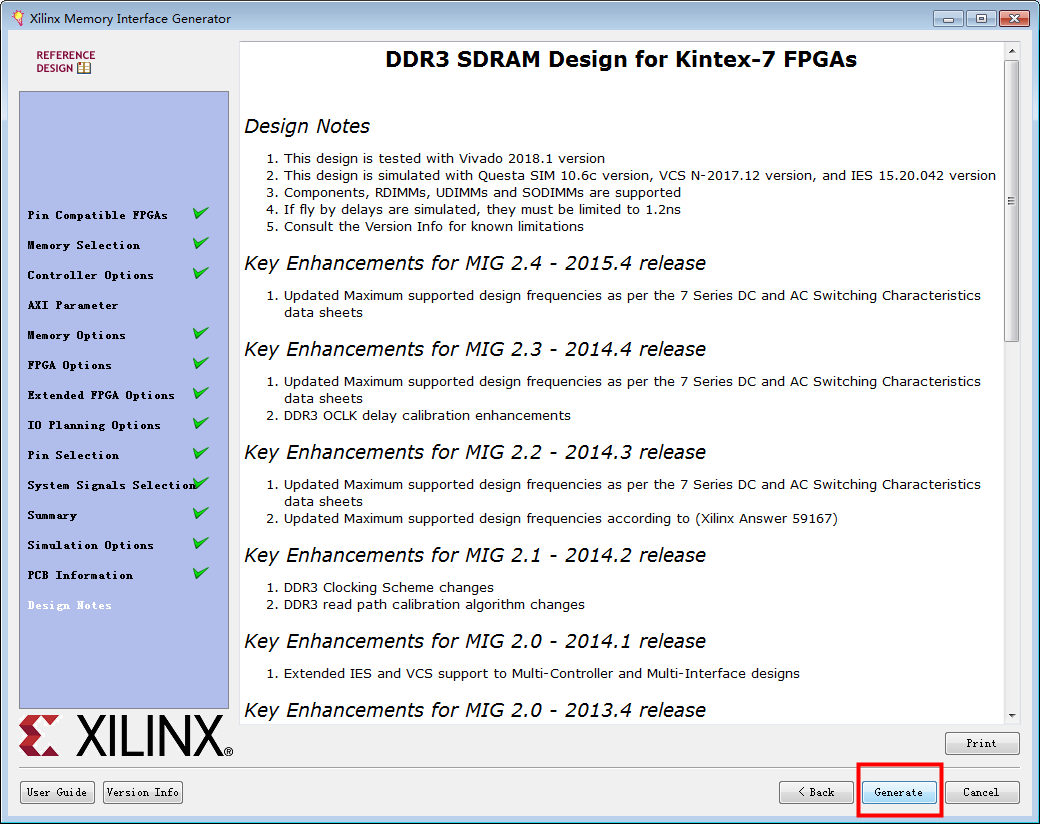

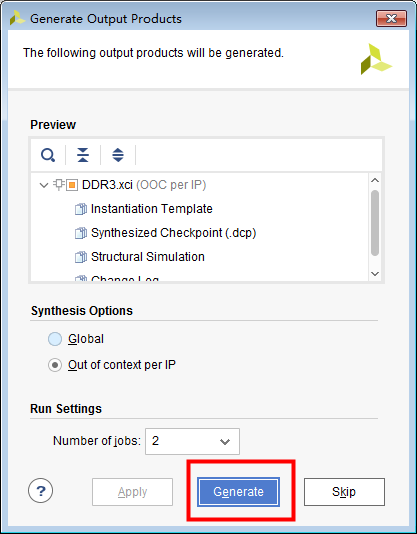

点击“Generate”生成MIG控制器。

四、生成文档

点击“Generate”,生成MIG控制器相关的设计文档。

以上就是基于Xilinx 的K7 DDR3 IP核的生成配置过程。