本文转载自:十年老鸟的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

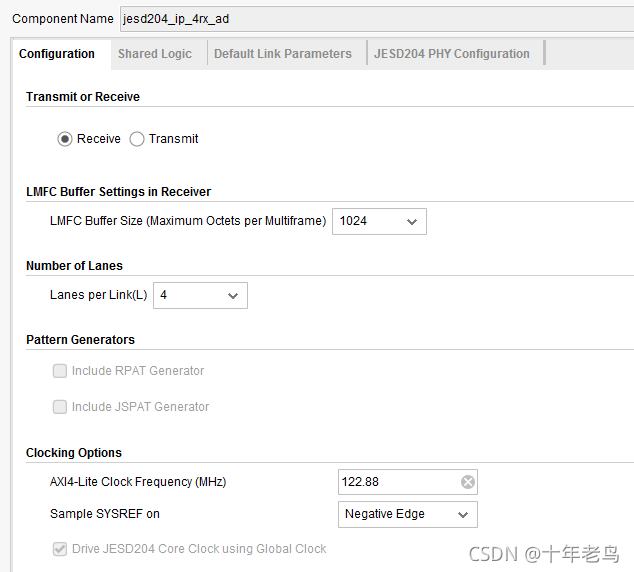

IP核配置

1、IP核为接收功能

2、LMFC buffer设定为最大

3、4条lane

4、sysref下降沿采样 (前面的帖子有说明为什么下降沿)

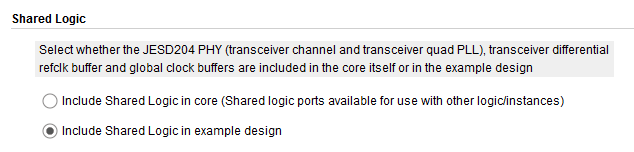

1、选择第二种,保持更大灵活性(不然更多的功能被包在了IP核中)

1、SYSREF always 前面博文有介绍

2、不开扰码

3、F K参数与外面transceiver器件设定相匹配

4、SYSREF Required on Re-Sync 前面博文有介绍

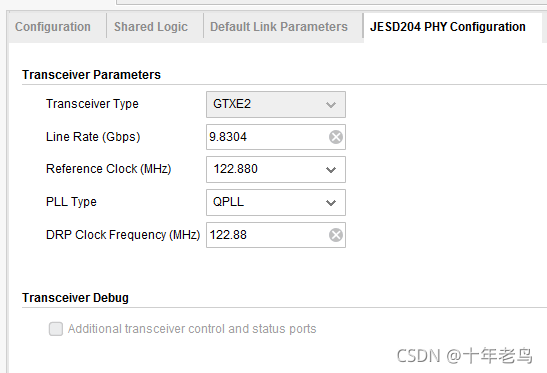

1、线速率 9.8304Gbps

2、参考时钟 122.88

3、DRP时钟 122.88

生成IP核后,右击IP核,点击example design,一个tb工程就自动生成了。

testbench工程

以下是xilinx jesd手册文档描述的接收testbench工程

这里要注意,因为例程中M = LANE数,相当于1条lane对应1个转化器

而一条lane 数据输入或输出接口是 在245.76M下的32bit输出

而转化器是491.52下的14(16)bit输入或输出。

因此相当于一个时钟下两个采样点并行输入输出。

在接收校验模块中 jesd204_ip_4rx_ad_sig_chk.v

在一个clk时钟下接收到了2个数据,即可说明上述说法是正确的

//Channel 0

signal0_sampl0_expected <= sine_lut64_14bit[index0];

signal0_sampl1_expected <= sine_lut64_14bit[index0+1];

signal0_cntrl0_expected <= index0; //clipped to two bits

signal0_cntrl1_expected <= index0+1; //clipped to two bits

index0 <= index0+2;

(在实际应用中,一般是存在IQ两路数据的,I/Q分别都需要一个转换器,4个转换器相当于2对IQ了)

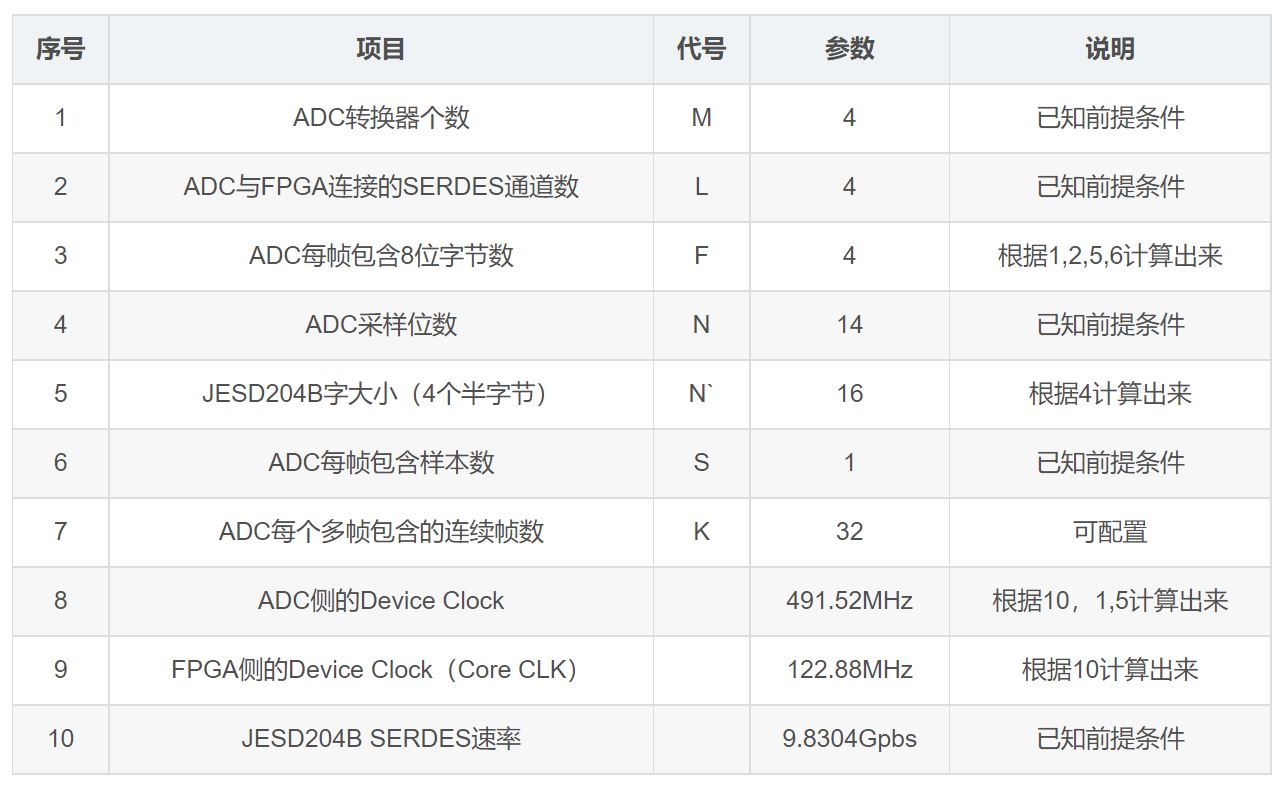

相关计算过程如下:

1、F的值根据 MSN`/(8L) = 4116/(84) = 2

1、serdes速率为9.8304Gbps,并行数据宽度为32位,core clock为 9.8304G * 0.8 / 32 = 245.76MHz

2、8位字符时钟character clock为

245.76MHz*4 = 983.4MHz

3、Frame clock 为491.52MHz (F=2,四个字节一个frame)

4、Multi - Frame clock 为 491.52MHz/32 = 15.36MHz

5、SYSREF周期数必须是Multi - Frame clock的整数倍分频,可以更小,不能更大。

(This generate a periodic SYSREF with period = 4 Multiframes 3.84)

部分代码解读

下面涉及两个任务

Task:rx_stimulus_send_column 将字节经过8B10B编码后,

通过Task:rx_stimulus_send_10b_column发送出去。其中里面还包含一个8B10B编码函数,因为相对来说比较固定,这里不做解读,只要知道经过了这个函数后,8bit就变成了10bit即可。

ILA 4个多帧,一个多帧(F = 2 K = 32)64字节,那么4个多帧256个字节

------------------------------多帧1------------------------------

字节1 : K28.0 8’h1C (R)

字节2-63: 数字:0 – 61 (D)

字节64 : K28.3 8’h7C (A)

------------------------------多帧2------------------------------

字节1 : K28.0 8’h1C (R)

字节2 : K28.4 8’h9C (Q)

字节3 : pDID 8’h55

字节4 : {pADJCNT, pBID} 4’h0 4’hA

字节5 ([4:0]) : LANEID(如果有4个lane,那么每个lane这个字节分别为0-3)

([7:5]) : {1’b0, pADJDIR, pPHADJ} 0 0

字节6 : {pSCR, 2’b0, pL} pSCR = 0 pL = Lane的个数- 1

字节7 : pF – 1 pF即参数F

字节8 : pK – 1 pK即参数K

字节9 : pM = Lane的个数 – 1

字节10 : {pCS, 1’b0, pN} pCS = 2’d2 pN = 5’d13 查询一下,AD位数14bit

字节11 :{pSUBCV, pNt} 3’b001 5’d15

字节12 :{pJESDV, pS} 3’b001 5’d0

字节13 :{pHD, 2’b0, pCF}

字节14 :{pHD, 2’b0, pCF} 1’b0 5’d1

字节15 :{ pRES1} 8’h5A

字节16 :{ pRES2} 8’hA5

字节17 :prechecksum + LANEID

字节18-63 :数字:0 – 46

字节64 : K28.3 8’h7C (A)

------------------------------多帧3------------------------------

字节1 : K28.0 8’h1C (R)

字节2-63: 数字:0 – 61 (D)

字节64 : K28.3 8’h7C (A)

------------------------------多帧4------------------------------

字节1 : K28.0 8’h1C (R)

字节2-63: 数字:0 – 61 (D)

字节64 : K28.3 8’h7C (A)

发射端在检测到sync后,遇到sysref上升沿开始发送ILA。红色箭头所示

接收端收到了4个多帧后(前后带K码),很快tvalid信号拉高,则可以数据接收准备好,可以取数据了

tb中的axi_write如果IP核中配置正确的话下面代码在实际应用中可以不需要

// 0x008: Support ILA

axi_write(2,32'h00000001);

// 0x00C: Scrambling dissabled

axi_write(3,32'h00000000);

// 0x010: Sysref once

axi_write(4,32'h00000001);

// 0x014: Tx Only register

// 0x018: Test mode = Normal operation

axi_write(6,32'h00000000);

// 0x020: Octets per Frame F=2

axi_write(8,32'h00000001);

// 0x024: Frames per Multiframe K=32

axi_write(9,32'h0000001F);

// 0x028: Lanes in use

axi_write(10,32'd15);

// 0x02C: Device subclass 1

axi_write(11,32'h00000001);

// 0x030: Rx buffer delay

axi_write(12,32'h00000000);

// 0x034: Error reporting via ~sync

axi_write(13,32'h00000000);

只需要对 写这个即可

axi_write(1,32'h00000001);

看明白了接收,那么发射也就不难了,这里就不再说明了