本文转载自:FPGA技术实战的CSDN博客

引言:在上一篇文章中,我们介绍了DCI的一些理论知识,本文我们重点介绍一下内容:

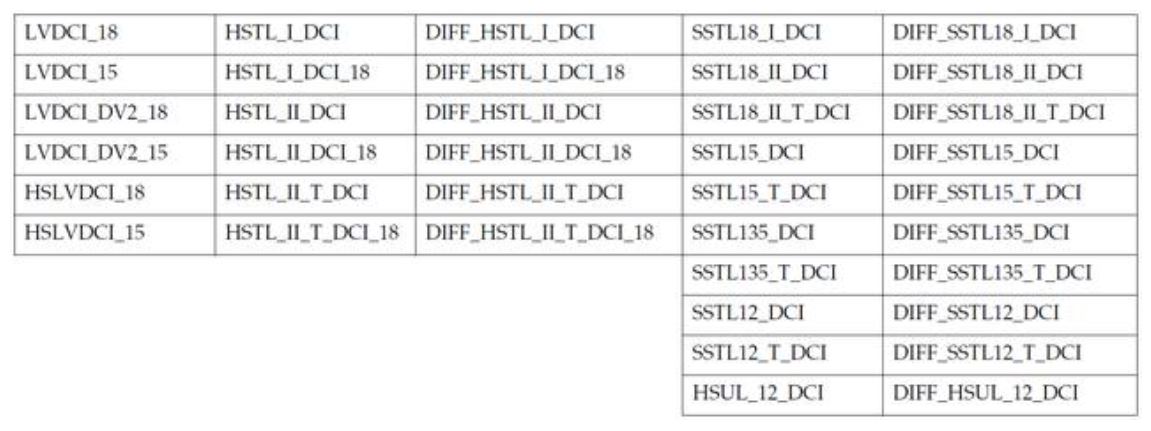

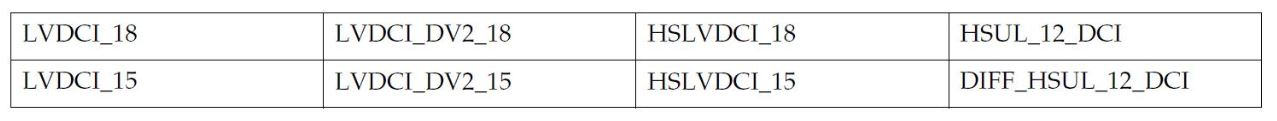

1.7系列FPGA DCI I/O标准

7系列FPGA所有DCI I/O标准如图1所示。

图1、系列FPGA所有DCI I/O标准

为了在7系列FPGA中正确使用DCI:

1)基于I/O bank所使用的IOSTANDARDs,VCCO管脚必须连接到恰当的VCCO电压;

2)正确的DCI I/O缓冲器必须在软件中使用,可以通过使用IOSTANDARD属性或者在HDL代码中例化;

3)DCI标准要求连接外部参考电阻到多功能管脚(VRN和VRP)。当VRN和VRP连接外部参考电阻后,则这两个管脚则不能用作一般用途I/O。管脚VRN必须通过参考电阻上拉到VCCO,管脚VRP必须通过参考电阻下拉到GND。在DCI级联应用中,从DCI I/O bank的VRN和VRP管脚无需连接外部参考电阻,可以用作一般用途I/O。

带有控制阻抗驱动器DCI标准可以用在只作为输入的信号管脚。对于这种情况,如果这些管脚在给定的I/O bank内是唯一使用DCI的管脚,则该bank不要求连接外部参考电阻到VRN和VRP管脚,此时,该bnak内的VRN和VRP管脚可以用作一般用途I/O。

DCI输入不要求外部参考电阻连接至VRN和VRP的I/O标准如图2所示。

图2、DCI输入不要求外部参考电阻连接至VRN和VRP的I/O标准

4)外部参考电阻的取值应该根据想要的输出驱动器阻抗或者分立端接阻抗进行选择。例如,如果使用LVDCI_15,为了达到50Ω输出驱动器阻抗,VRN和VRP管脚分别连接50Ω参考电阻。当使用SST15_T_DCI标准,为了达到50Ω戴维宁等效端接(R)连接到VCCO/2,外部参考电阻应该为100Ω(2R)。

5)遵循以下DCI I/O bank规则:

2.DCI使用举例

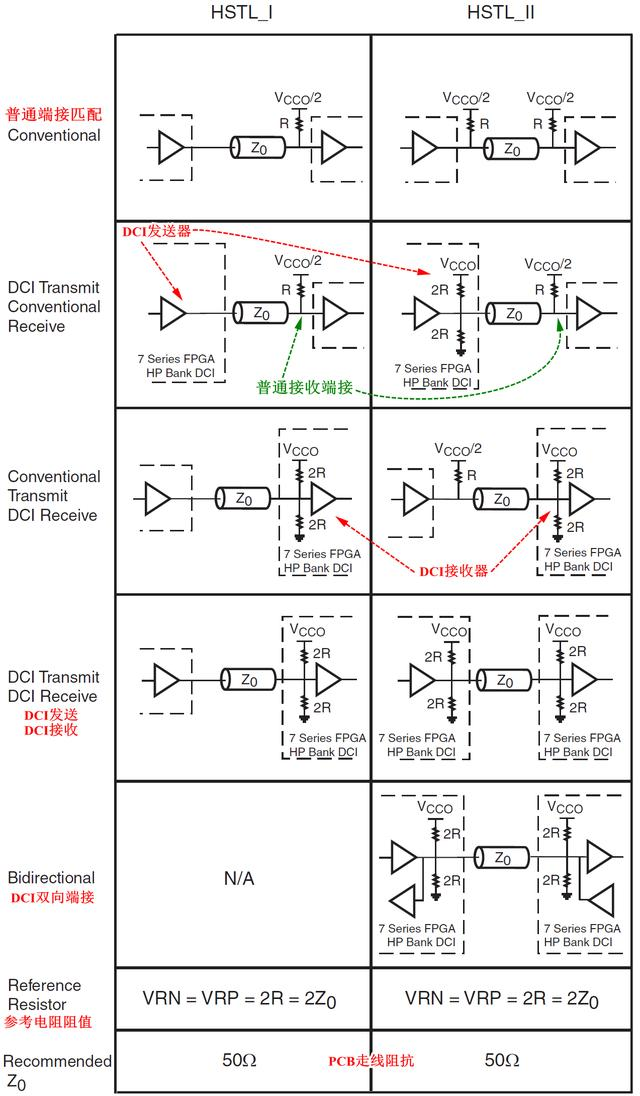

图3举例了HSTL_I_DCI和HSTL_II_DCI I/O标准使用。

图3、HSTL DCI使用举例

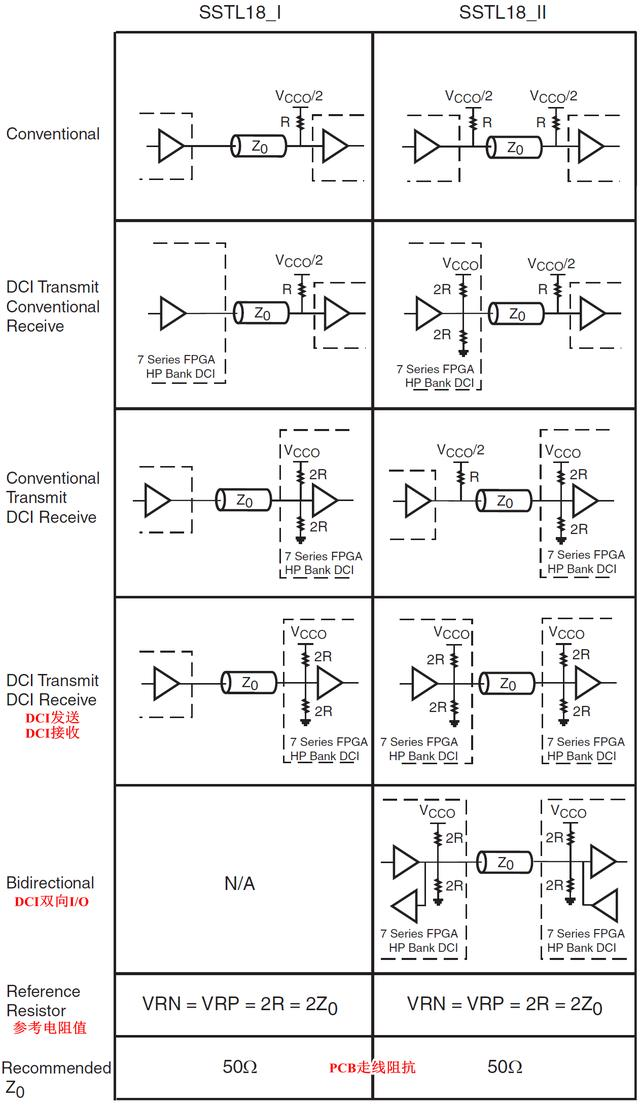

SSTL DCI使用举例如图4所示。

图4、SSTL DCI使用举例

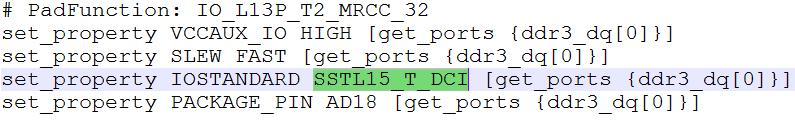

DDR3 数据I/O DCI使用举例如图5所示。

图5、DDR3数据I/O DCI标准使用举例