本文转载自:孤独的单刀的CSDN博客

1、$finish

系统任务$finish的作用是退出仿真器,结束仿真过程。格式:

$finish

$finish(n)

当$finish带参数时,如(2),根据不同的参数值,系统输出的特征信息:

0:不输出任何信息;

1:输出当前仿真时刻和位置;

2:输出当前仿真时刻、位置和仿真过程中所用的memory及CPU时间的统计。

当$finish后面不带参数时,则默认参数为1。

2、$stop

$stop任务得作用是把EDA工具(例如仿真器)置为暂停模式,在仿真环境下给出一个交互式的命令提示符,将控制权交给用户。格式与$finish类似:

$stop

$stop(n)

用法同样与$finish类似:当$stop带参数时,如(2),根据不同的参数值,系统输出的特征信息:

0:不输出任何信息;

1:输出当前仿真时刻和位置;

2:输出当前仿真时刻、位置和仿真过程中所用的memory及CPU时间的统计。

当$stop后面不带参数时,则默认参数为1。

3、实际应用

这两个系统任务在不同的编译器下使用可能有细微的区别,接下来分别在vivado仿真器和modelsim仿真器中进行验证。

3.1、$stop在vivado环境

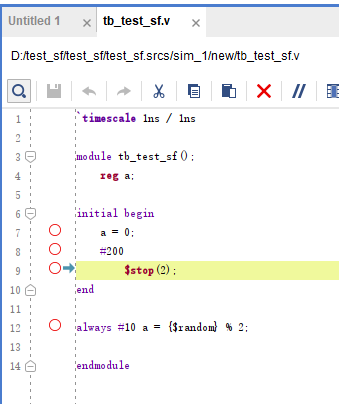

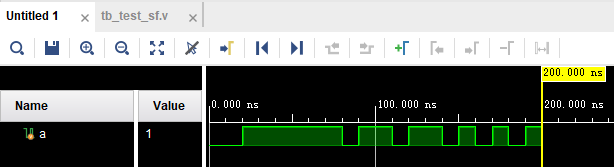

使用如下testbenchn进行验证:信号a每20ns产生0或1,在200ns处使用$stop暂停。

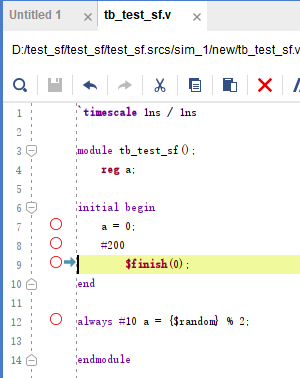

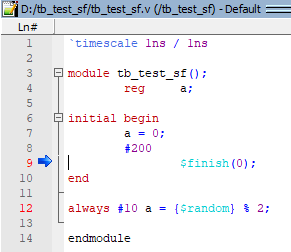

`timescale 1ns / 1ns

module tb_test_sf();

reg a;

initial begin

a = 0;

#200

$stop(0);

end

always #10 a = {$random} % 2;

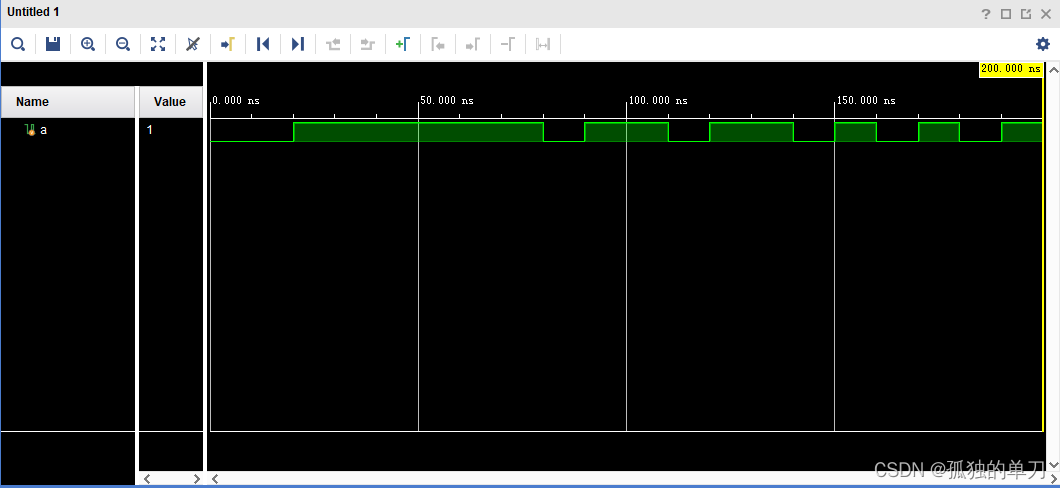

endmodule点击RUN ALL按钮,波形仿真停留在200ns处:

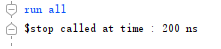

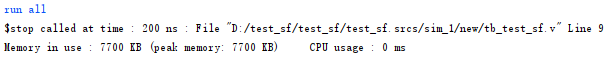

TCL窗口打印的信息:

此时可以继续仿真。

将$stop(0)内参数改为1:

仿真结束后自动跳转到testbench的$stop语句处,波形依旧停留在200ns处。

TCL窗口打印的信息变多了一些:

将$stop(0)内参数改为2:

仿真结束后自动跳转到testbench的$stop语句处,波形依旧停留在200ns处。

TCL窗口打印的信息多了memory和CPU的使用情况:

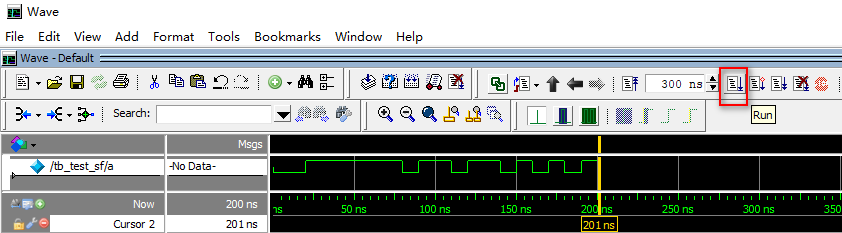

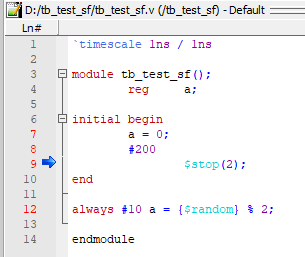

3.2、$stop在modelsim环境

依然使用上面的TB进行验证,将$stop(0)内参数设置为2。

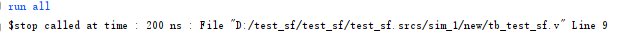

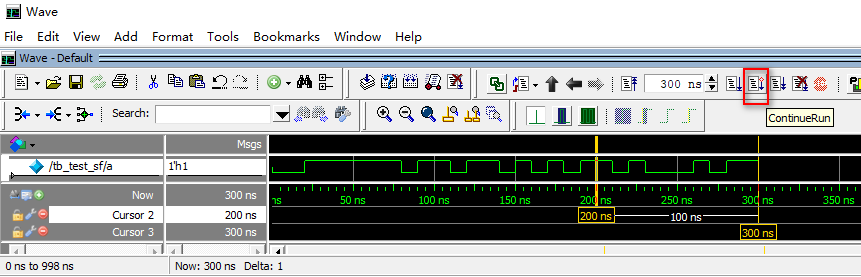

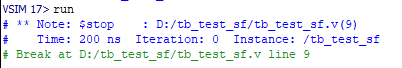

点击仿真300ns,仿真结束后自动跳转到testbench的$stop语句处,波形则停留在200ns处。

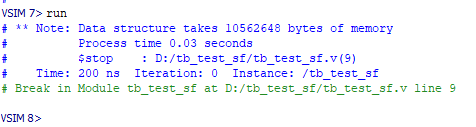

窗口打印的信息:

此时,若点击继续仿真按钮,则会在仿真到300ns处暂停,接下来也可以继续进行仿真。

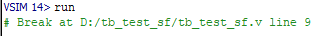

接下来将$stop(2)内参数改为1,其他与参数为2的情况一致,只是窗口打印没有了memory和CPU的使用情况:

将$stop(1)内参数改为0,仿真暂停后并没有自动跳转到testbench的对应界面,且打印信息更少:

3.3、$finish在vivado环境

使用如下testbenchn进行验证:信号a每20ns产生0或1,在200ns处使用$finish终止仿真。

点击RUN ALL按钮,波形仿真停留在200ns处:

TCL打印信息:

仿真并不会停止,此后仍可以继续仿真。

将$finish(0)内参数改为1:

仿真结束后自动跳转到testbench的$finish语句处,波形依旧停留在200ns处(后续也仍可仿真)。

TCL窗口打印的信息变多了一些:

$finish(2)的情况基本一致,只不过打印信息多了memory和CPU的使用情况:

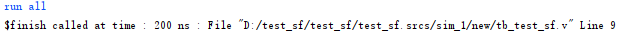

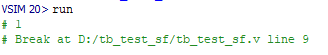

3.4、$finish在modelsim环境

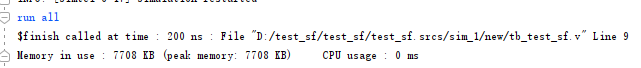

依然使用上面的TB进行验证,首先将$finish()内参数设置为0:

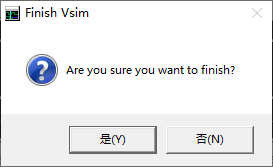

弹出提示框:

若选择是则会退出仿真并关闭modelsim软件;选否则会将将波形在200ns处暂停,后续可以继续仿真,窗口自动跳转到testbench的$finish语句处:

窗口打印信息:

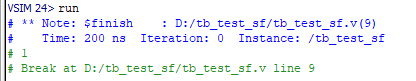

$finish(1)的情况基本与$finish(0)一致,只是打印信息的差别:

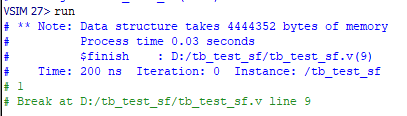

$finish(2)页是打印信息的差别:

4、总结

$finish可以终止仿真,一般用在仿真的结尾处。例如完成某些特定激励的仿真后将仿真终止,防止仿真不停地运行

$stop可以暂停仿真,一般用来在某个特定的时间暂定仿真

$stop和$finish常用在测试模块的initial模块中,配合时间延迟用来控制仿真的持续时间