本文转载自:FPGA的现今未

工作时间,前面介绍过就是有任务停留在该模块的时间。通常定义一个任务计数器,模块进来一个任务加1计数,完成或者输出一个任务就减1计数,该计数器不为0的时间就是工作时间。然后对任务计数器不为0的时间计数就得到了工作时间。如果该模块满负荷工作,那么他得到的工作时间的计数一定是0xBEBC200,也就是200M。

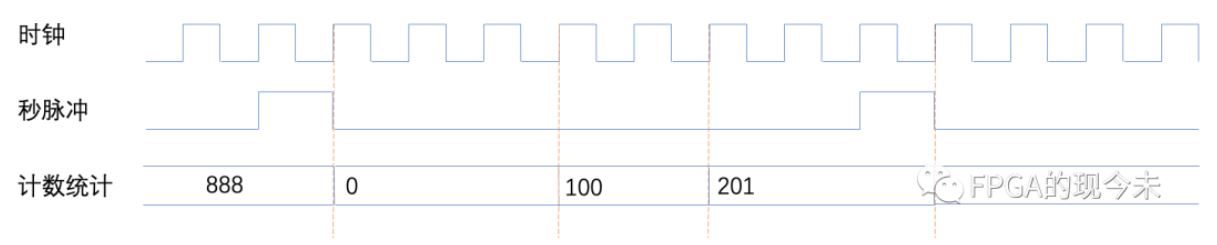

数据发送时间和反压时间,这2个的计数非常简单,数据发送的时间就是有data_vld的时间。反压时间,就是统计afull信号拉高的时间,只是要记得需要用秒脉冲来锁存。

有了上述的3个时间,加上上一篇的分析,就可以得到FPGA或者某一个模块是否处于满负荷状态,并计算出在满负荷状态下的最大性能,或者找出系统中的性能瓶颈点,通常是性能最低的某个模块。

总之性能是设计出来的,在方案阶段就需要设计出最大的性能,并在验证的过程中确认性能是否达标,而不是等到上板测试阶段才来找性能瓶颈点。