本文转载自:FPGA技术实战的CSDN博客

引言:本章继续介绍7系列FPGA收发器TX结构,通过本文可以学习以下内容:

TX时钟输出控制结构

TX配置驱动器结构

1.TX时钟输出控制结构

1.1概述

TX时钟分频器控制模块有两个主要的组件:串行时钟分频器控制模块和并行时钟分频器及选择器控制。图1给出了时钟分频器和选择器详细的结构。

图1、时钟分频器和选择器详细的结构

在图1中,注意一下几点:

[1]. TXOUTCLKPCS和TXOUTCLKFABRIC是冗余输出。TXOUTCLK时钟一般用于FPGA内部逻辑设计。

[2]. REF_CTRL选项由软件自动控制的,用户不可选择。用户只能使用使用IBUFDS_GTE2中的O或者ODIV2通过CMT、BUFH或者BUFG输出到FPGA逻辑资源。

[3]. IBUFDS_GTE2可以看做冗余时钟,增加了收发器时钟方案的灵活性。

[4]. CPLL在GTXE2_CHANNEL/GTHE2_CHANNEL中只有一个。来自GTXE2_COMMON/GTH2_COMMON的QPLL可以用于收发器通道(之前文章有详细介绍)。

[5]. /2或者/4分频器模块由GTXE2_CHANNEL/GTHE2_CHANNEL的TX_INT_DATAWIDTH属性控制。TX_INT_DATAWIDTH = 0时,/2用于收发器内部2字节数据路径;TX_INT_DATAWIDTH = 1时,/4用户收发器内部4字节数据路径。

[6]. /4或者/5分频器模块由GTXE2_CHANNEL/GTHE2_CHANNEL的TX_DATA_WIDTH属性控制。TX_DATA_WIDTH = 16,32,64时,选择/4分频器;TX_DATA_WIDTH = 20,40,80时,选择/5分频器。

1.2 串行时钟分频器

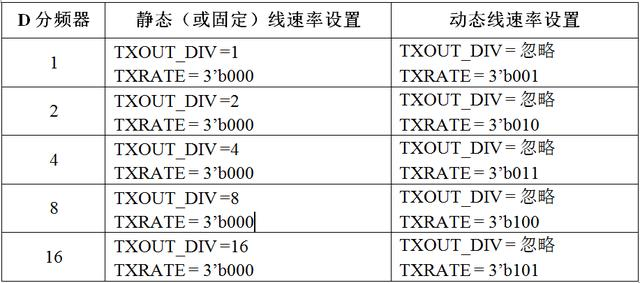

每个发送器PMA模块有一个D分频器,用来将PLL时钟分频为较低的线速率要求的时钟。该分频器可以用于设置为固定线速率或者动态线速率。静态(或固定)线速率和动态线速率配置如图2所示。

图2、静态(或固定)线速率和动态线速率配置

1.3 并行时钟分频器和选择器

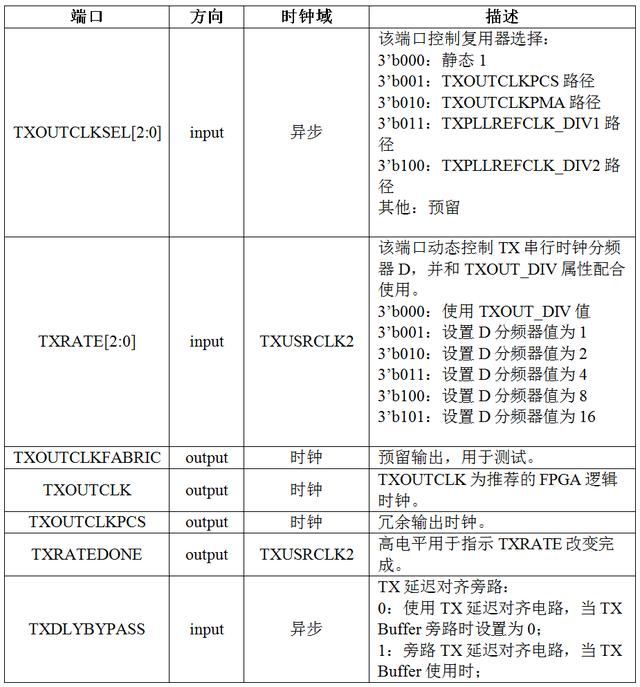

从TX时钟分频器模块输出的并行时钟可以用于FPGA逻辑时钟,Xilinx推荐的FPGA逻辑时钟为TXOUTCLK(该时钟应用方案在第(六)篇有介绍)或者使用MGTREFCLK管脚输入时钟直接作为FPGA逻辑资源时钟。TX时钟输出控制端口定义如图3所示。

图3、TX时钟输出控制端口定义

2.TX配置驱动器

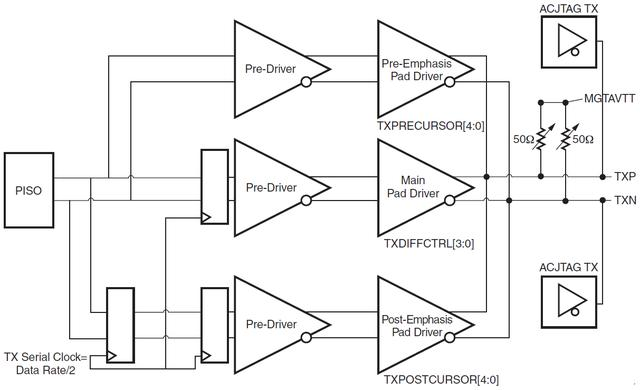

图4、TX配置驱动器模块

GTX/GTH收发器的TX驱动器是一个高速电流模式差分输出缓冲器。为了最大信号完整性,它包括以下特性:

差分电压控制

Pre-cursor和Post-cursor发送器预加重

校准端接电阻

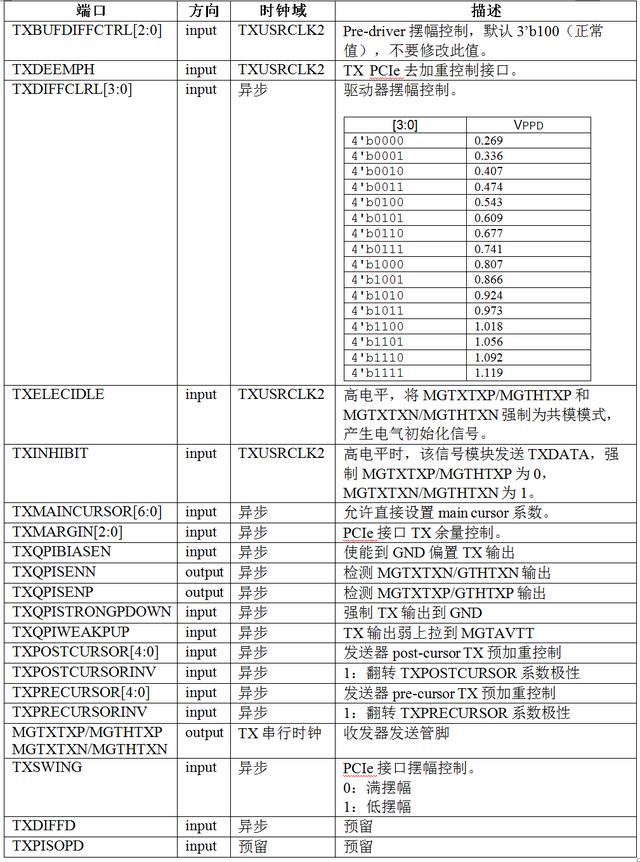

TX配置驱动器端口如图5所示。

图5、TX配置驱动器端口