本文转载自:Vuko-wxh

前言

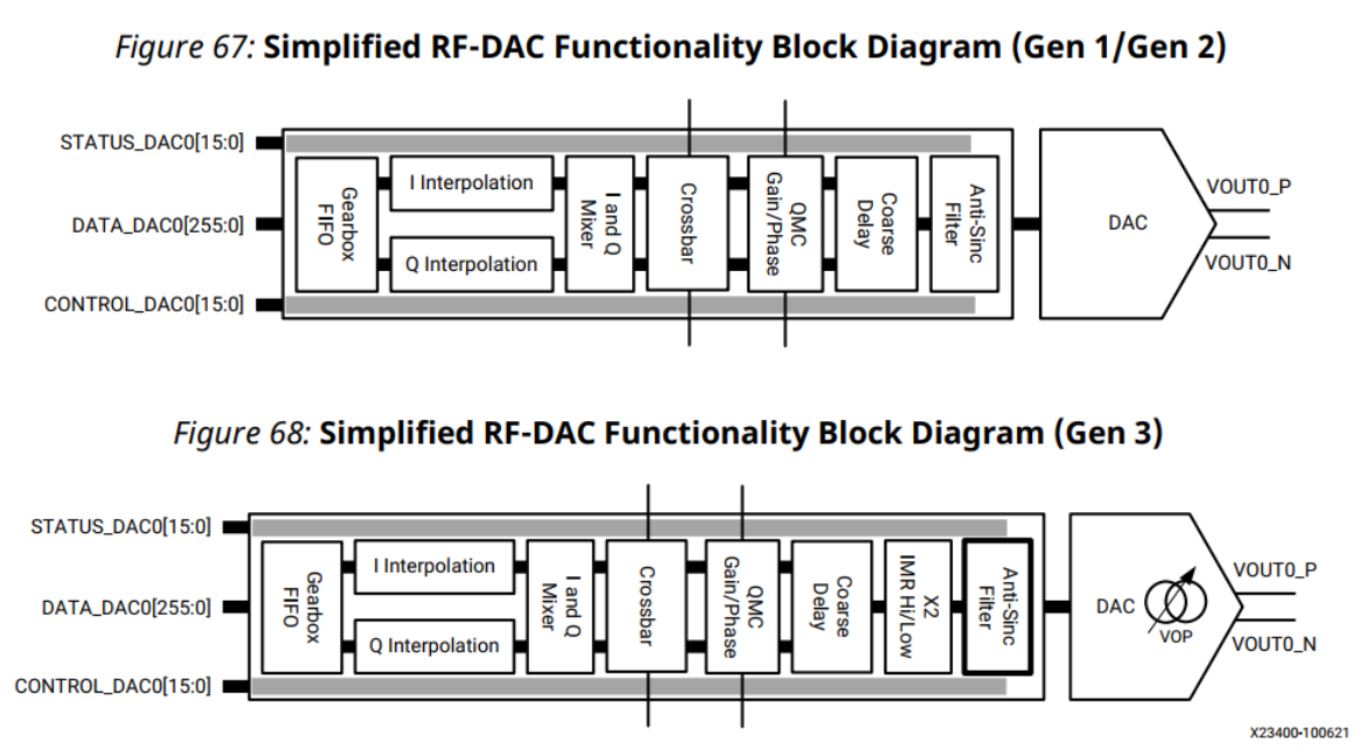

RFSoC中最重要的部分是射频直采ADC和DAC的配置,因此了解内部相关原理结构可以帮助我们更好理解相关功能配置参数含义。本文参考官方手册,主要对RF-DAC 模拟输出进行介绍。

RF-DAC简介

每个 RF-DAC 块都包含一个完整的时钟支持结构,带有一个 PLL 和必要的同步逻辑。 tile 中的每个 RF-DAC 都有一个高度可配置的 FIFO,允许内部互连逻辑直接高速访问 RF-DAC。

某些功能只能在一个 tile 中的 RF-DAC 配对时执行。 偶数 RF-DAC 用于 I 数据路径,奇数 RF-DAC 用于 Q 数据路径。

一个 tile 的所有可用内置功能和一个 tile 中的每个 RF-DAC 都是用户可编程的。 Vivado IDE 中的RF 数据转换器内核配置界面和 RFdc 驱动程序 API 可用于配置 RF-DAC 的数字和模拟功能。

RF-DAC 模拟输出

tile 中的每个 RF-DAC 都有自己的差分模拟电流输出缓冲器/驱动器。 输出电流是互补的; 两个电流之和始终等于 RF-DAC 的满量程电流。 数字输入代码决定了提供给负载的有效差分电流。 差分 RF-DAC 输出通常使用电容器进行交流耦合。 假设满足正确的共模偏置和负载阻抗要求,还支持 RF-DAC 输出直流耦合。

发送传递函数

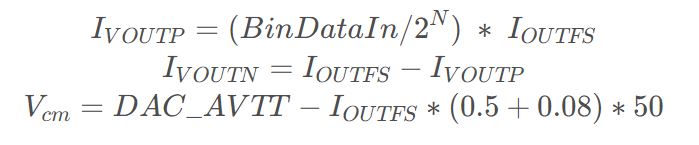

当所有数字输入位为高电平时,差分输出提供最大输出电流。

输出电流(使用二进制格式)显示在以下等式中。

其中:

BinDataIn = 14 位数字输入

IOUTFS = 满量程输出电流

Vcm 是每个 IVOUT leg上的共模电压

RF-DAC 输出电流模式(第 1 代/第 2 代)

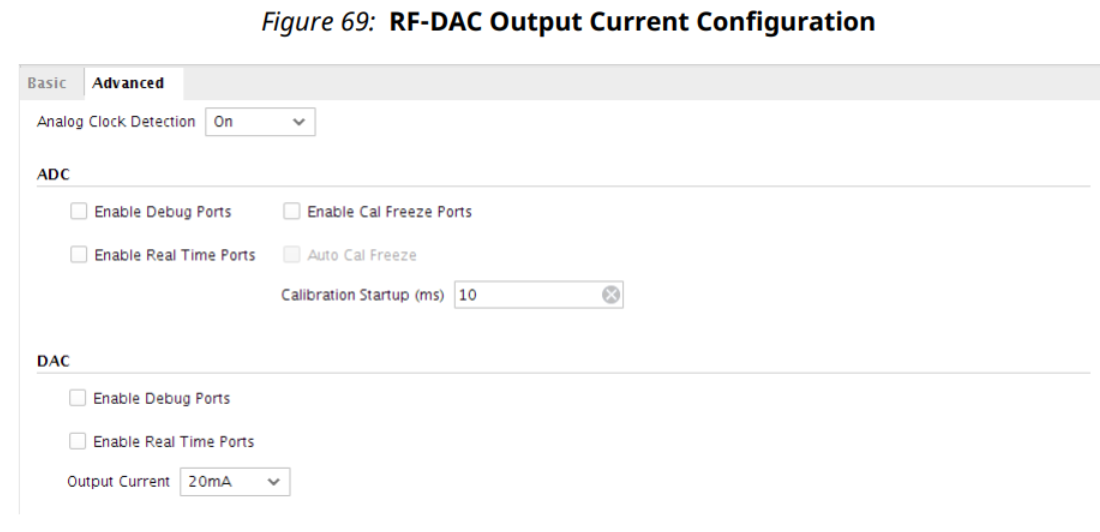

RF-DAC 输出电流是可配置的,可选择在 20 mA 或 32 mA 模式下工作。 在 20 mA 模式下,将 DAC_AVTT 设置为 2.5V,在 32 mA 模式下,将其设置为 3.0V 以保持线性性能。

可以在 IP 内核配置屏幕的 Advanced 选项卡中设置输出电流(见下图)。

RFdc Driver API Commands (Gen 1/Gen 2)

// 获取 RF-DAC Tile1、Block2 的输出电流为 32mA XRFdc_GetOutputCurr(ptr, 1, 2, XRFDC_OUTPUT_CURRENT_32MA);

可变输出功率 (VOP) (Gen 3)

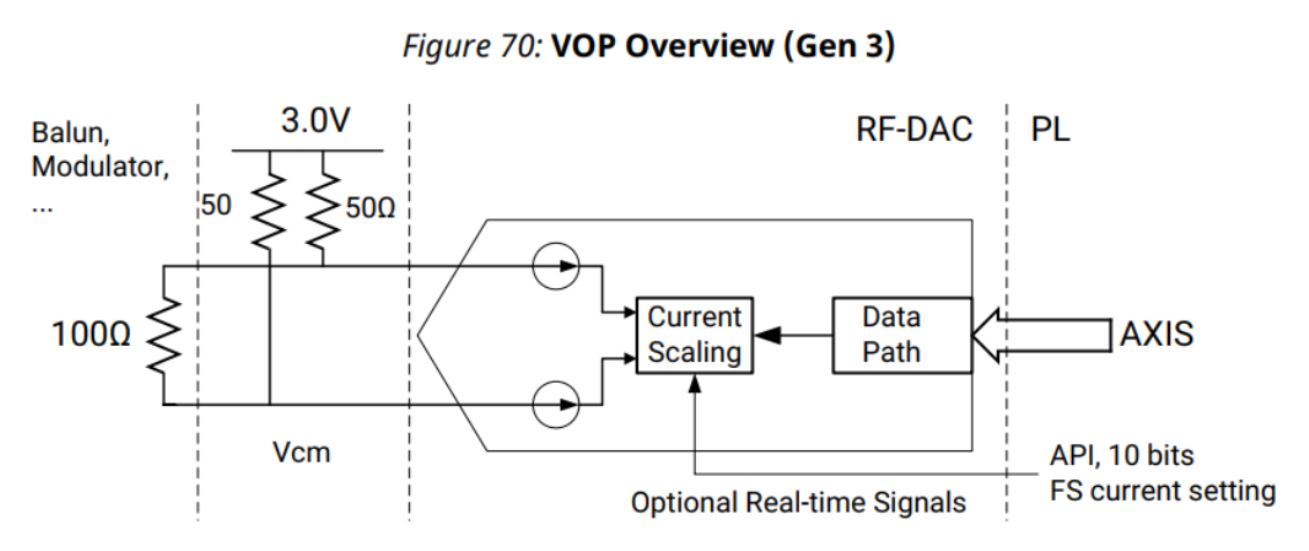

许多发射器系统包括可变增益放大器 (VGA) 级,允许在模拟域中放大或衰减信号。RF-DAC 模拟电路支持调整输出功率的能力,并与数字控制相结合以实现 RF-DAC 可变输出功率 (VOP) 功能。

VOP 详细信息(第 3 代)

下图显示了片上 VOP 功能。

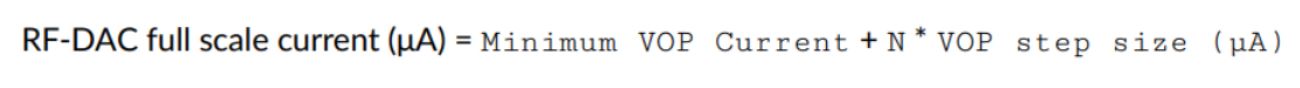

RF-DAC 的满量程电流可以通过以下方式得出:

其中 N = 0, 1, 2, …,受最大满量程电流限制。

为了避免增益急剧变化时对无线发射器信号链的潜在危害,API 设计为将一个大的跳跃分成几个小步骤,然后以一定的时间间隔依次更新 VOP。 步长约为当前 VOP 值的 ±10%。

启动期间的默认满量程电流由 IP 配置设置。

VOP 向前兼容性(第 3 代)

在 Gen 1 和 Gen 2 中,只有 20 mA (2.5V) 和 32 mA (3.0V) 模式可用。 Gen 3 IP 中提供了向后兼容模式,以适应现有的硬件设计。 在此模式下配置时,VOP 功能不再可用,RF-DAC 与 Gen 1 和 Gen 2 一样,在 DAC_AVTT 上输出 2.5V 电源时 20 mA 和 3.0V 电源时 32 mA。电源方案由片上所有瓦片共享,因此一个芯片可以使用 VOP 模式或 20/32 mA 模式。 不允许在一个磁贴上启用 VOP,在其他磁贴上启用 20/32 mA 模式。

一致的共模电压(第 3 代)

每个输出上的共模电压会随着 VOP 的变化而变化。 在需要直流耦合接口的应用中,通常需要固定 Vcm 以匹配外部设备。 以下两个选项可用于一致的共模电压:

向前兼容模式:在向前兼容模式下,共模电压与 Gen 1 和 Gen 2 一样固定,VOP 功能在此模式下不可用。

DC 耦合模式:RF-DAC DC 耦合模式在启用VOP 功能的同时固定共模电压。 在这种模式下,VOP 范围减小。

VOP 更新(第 3 代)

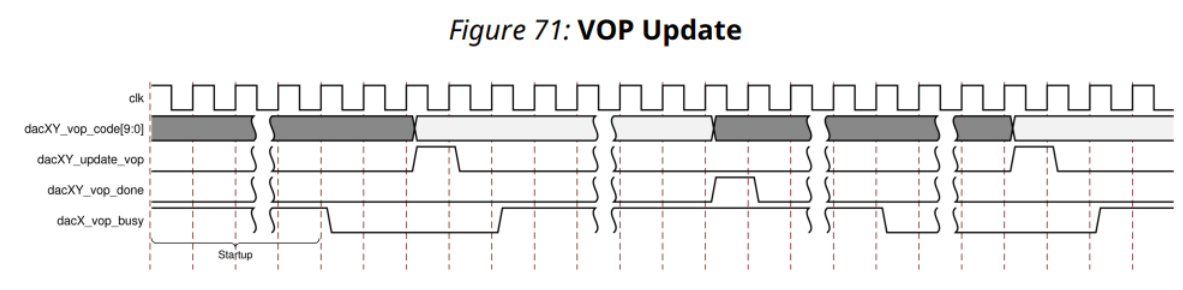

实时 VOP 信号接口使 RF-DAC 输出功率能够从 PL 进行调整。 更新输出功率的过程如下所示。

当 tile 的 dacX_vop_busy 输出为低电平时,可以将更新输入与所需的 VOP 代码一起置位。 VOP 代码是一个 10 位值,指示所需的满量程电流设置。 通过同时断言它们的更新输入,可以同时更新同一瓦片中的多个切片。VOP 代码应保留在 dacXY_vop_code 输入中,直到该过程完成。 在更新过程和瓦片启动期间断言忙碌信号。

当 VOP 更新成功完成时,完成输出 (dacXY_vop_done) 被断言。 两次 VOP 更新之间允许的最大跳变约为当前 VOP 值的 ±10%(以 mA 为单位)。 如果请求更大的跳转,转换器中的寄存器将不会被写入,并且完成信号也不会被断言。 如果需要更大的跳转,API 可用于设置正确的 VOP 值。

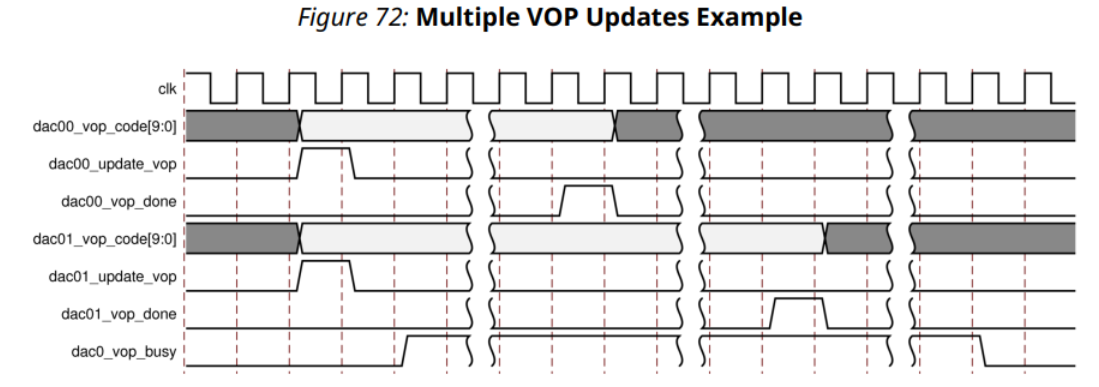

当多个 RF-DAC 通道同时被修改时,每个通道的 dacXY_vop_done 信号在该通道的 VOP 更新完成时被置位。 dacX_vop_busy 信号保持高电平,直到所有通道都已更新。 下面显示了同时更新转换器 0 中的通道 0 和通道 1 的示例。

RFdc 驱动器也可用于更新可变输出功率。 但是,驱动程序和实时信号方法是互斥的。 在使用 VOP 信号接口时,不应使用驱动器来修改输出功率。