版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/weiweiliulu/article/details/105774390

创建时钟是针对代码中主时钟而言,创建时钟之前需要知道代码中的主时钟都是什么,可以在综合以后,打开综合,然后在TCL 中输入命令:

report_clock_networks –name mynetwork

确定了主时钟,就可以对其创建时钟周期约束:

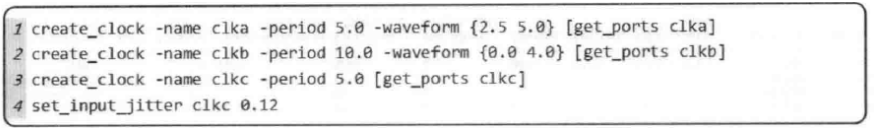

情形1:主时钟之间有明确的相位关系

-waveform不仅确定了时钟的占空比,也确定了时钟之间的相位关系。

(1)clka频率为200Mhz,等占空比。(初始化为1,waveform不是从0开始)

(2)clkb频率为100Mhz,占空比为40:60。

(3)clkc频率为200Mhz,等占空比,时钟抖动为120ps。

下面这些指令,可以在tools --- language templates ---- XDC 里面对应查找

create_clock -name <clock_name> -period <period> [get_ports <clock port>]

create_clock -period 8 -name i_x1_sys_clkp0 [get_ports i_x1_sys_clkp0]

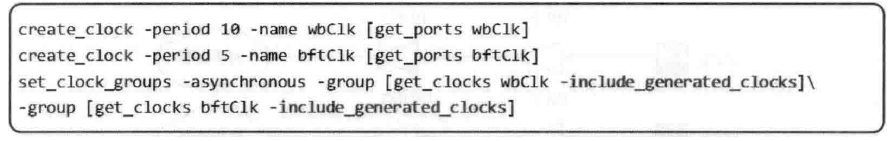

情形2:主时钟之间为异步关系

主时钟之间如果是异步关系,则需要通过set_clock_groups命令明确指定。

set_clock_groups -asynchronous -group <clock_name_1> -group <clock_name_2>

如果两个主时钟还通过MMCM或PLL生成了其他时钟,若这两个主时钟为异步关系,则它们的生成时钟也为异步关系。

set_clock_groups -asynchronous -group <clock_name_1> -group <clock_name_2>

创建两个时钟不相关

set_clock_groups -asynchronous -group i_x1_sys_clkp0 -group i_x4_sys_clkp0

创建两个时钟不相关,其生产时钟也不相关

set_clock_groups -asynchronous -group [get_clocks i_x1_sys_clkp0 -include_generated_clocks] -group [get_clocks i_x4_sys_clkp0 -include_generated_clocks]