作者:作者:碎碎思,来源:OpenFPGA

绪论

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题,不知道大家有没有遇到,就是新设计的自定义 RTL 文件无法快速的添加到Block Design中,一种方式是通过自定义IP,但是一旦设计的文件有问题就需要重新修改,同时需要控制接口时候还需要在AXI总线模板基础上进行修改,再同时繁琐的步骤也让人“望而却步”。下面介绍一种简单的方式。

我目前使用的是 Vivado 2019.1、2020.2,但据我所知,此功能几乎适用于 Vivado 的所有版本(如果不正确,请随时在后台更正)。

创建 Vivado 项目

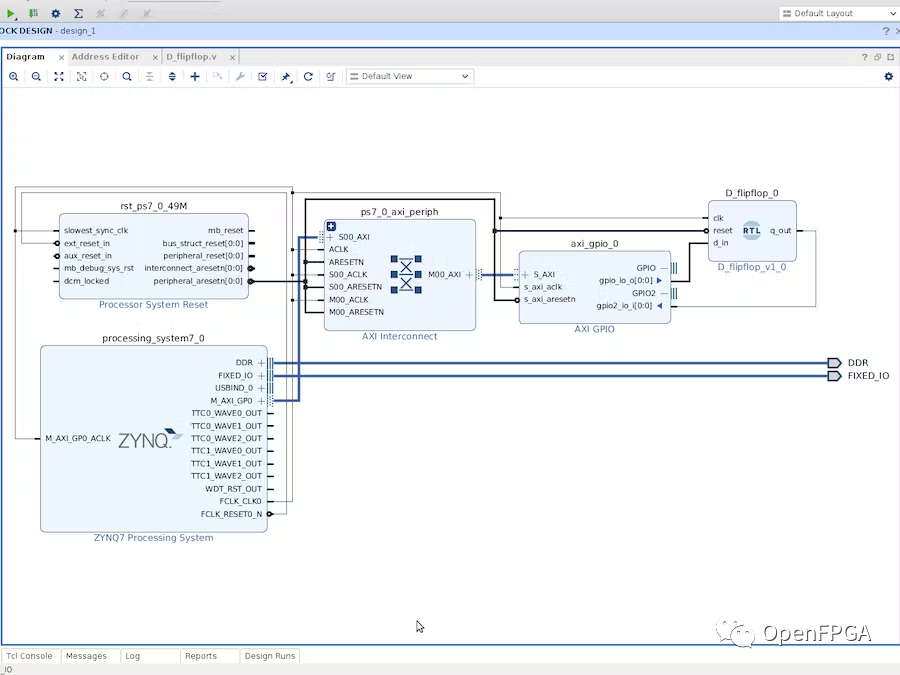

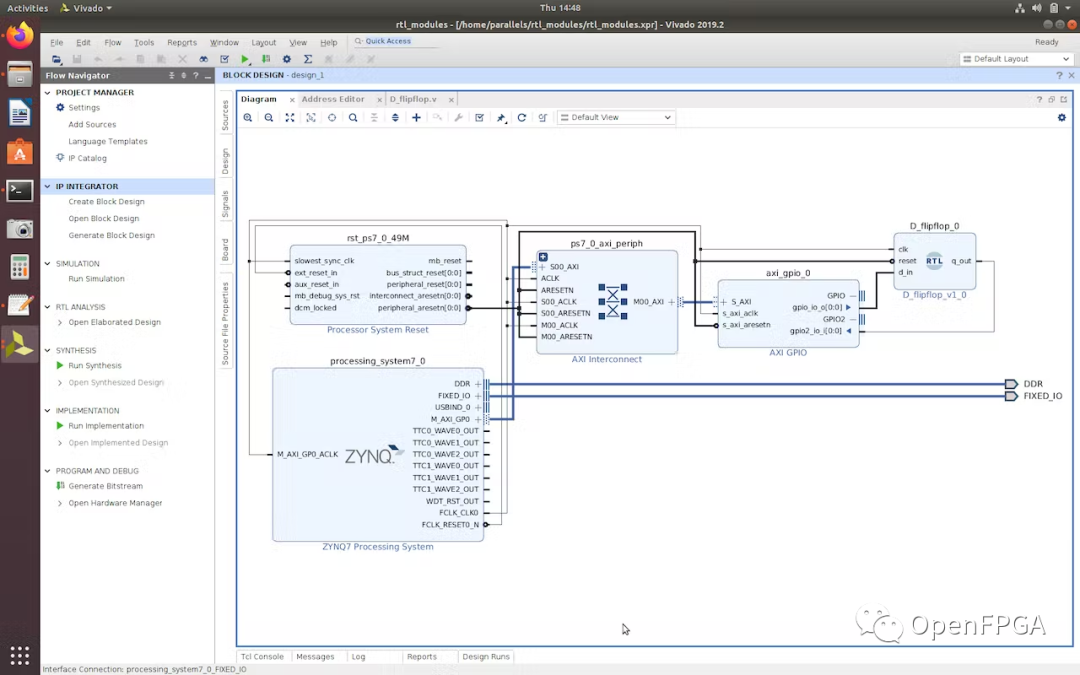

为了开始这个例子,我创建了一个基于 Zynq 的新 Vivado 项目(这只是我的例子,但这个项目的内容并不特定于任何特定的 FPGA 开发板),同时这个项目中包括一个通过AXI-Lite控制的自定义RTL。

添加设计文件并编写自定义 RTL

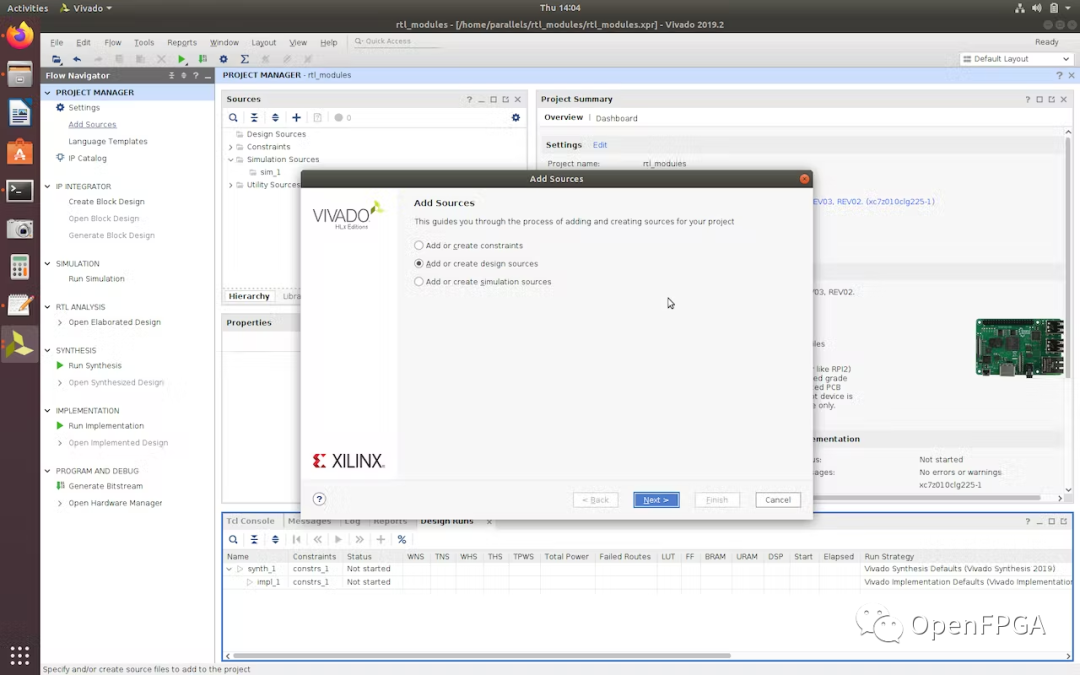

不用于仿真目的的自定义 RTL(即测试文件)都被视为 Vivado 中的设计源。使用 Flow Navigator 中的Add Sources选项并选择Add or create design sources ,然后单击 Next。

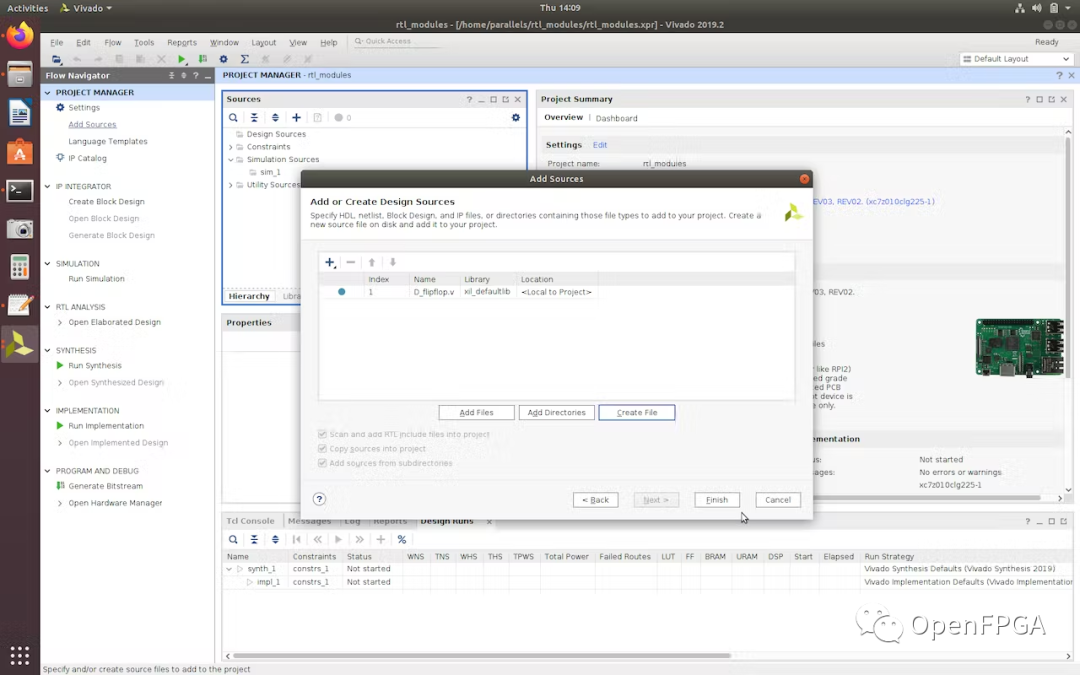

我们创建一个名为D_flipflop的新文件并添加了以下逻辑:

module D_flipflop( input clk, input reset, input d_in, output reg q_out ); always @ (posedge clk) begin if (reset == 1'b1) begin q_out <= 1'b0; end else begin q_out <= d_in; end end endmodule

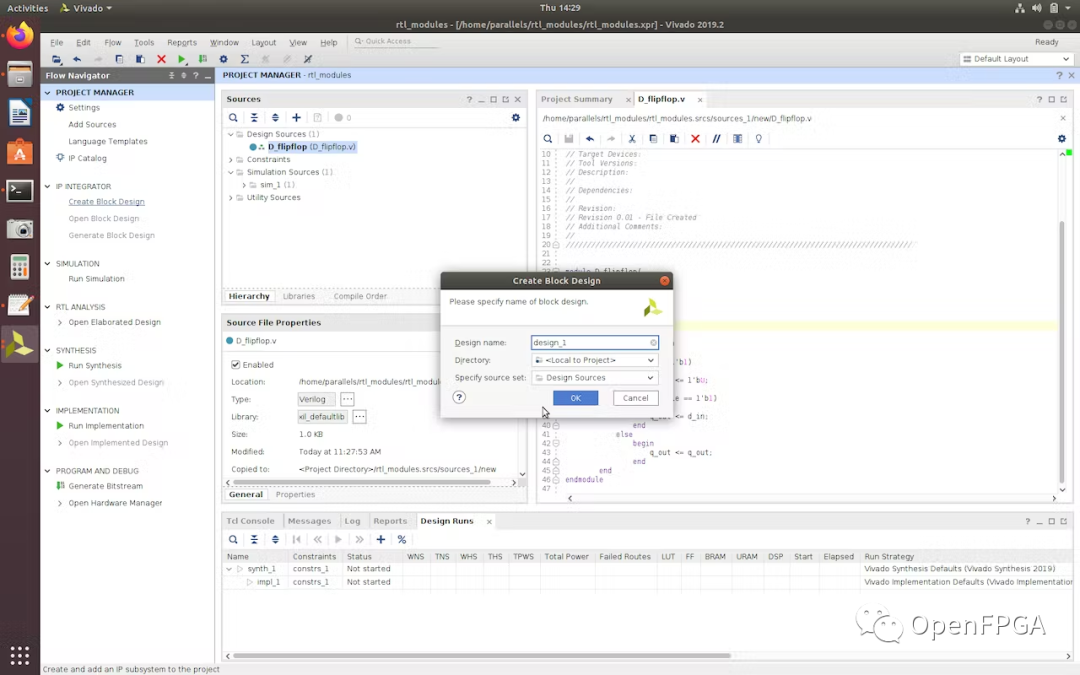

创建Block Design

使用 Flow Navigator 窗口中的Create Block Design选项,将新的Block Design添加到项目中。

将 Zynq 处理系统 IP 块添加到设计中,并运行自动设置或者自动连线。

将 RTL 模块添加到Block Design

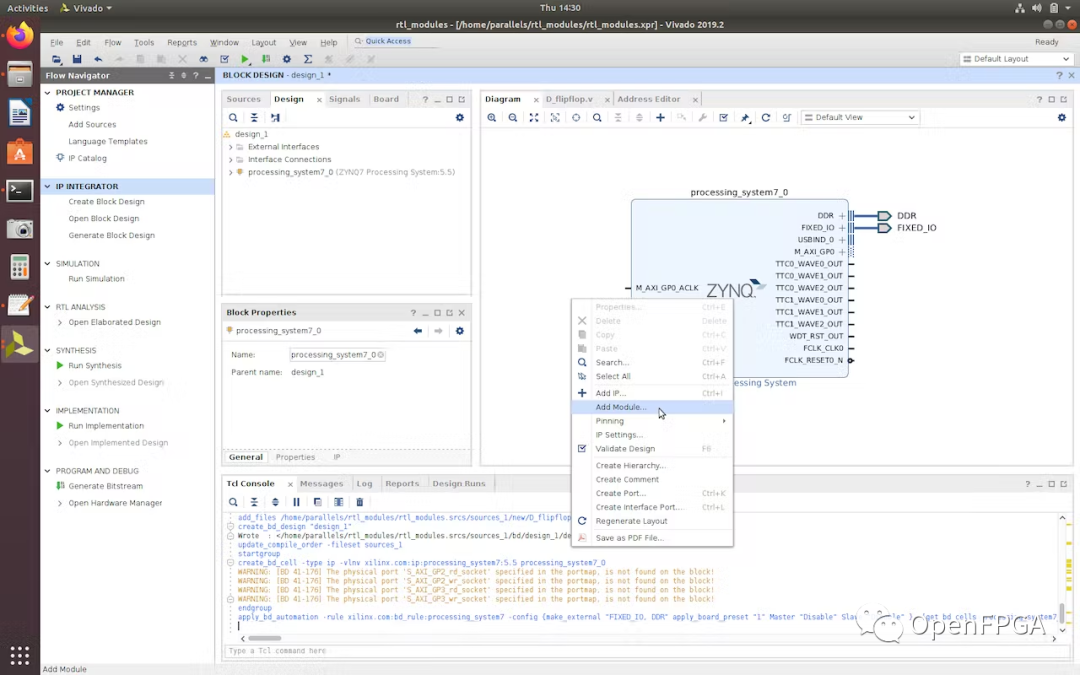

要添加我们在上一步中创建的 D 触发器的 RTL 模块,右键单击 Diagram 窗口空白处的任意位置,然后选择Add Module...选项。

Vivado 将自动显示它在当前项目中找到的所有有效 RTL 模块。由于写入或导入到当前项目中的模块是我们刚刚设计的 D 触发器,因此它是本例中的唯一选项。

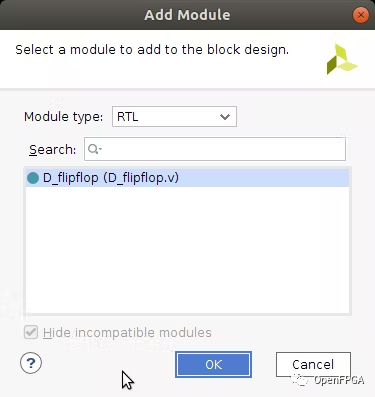

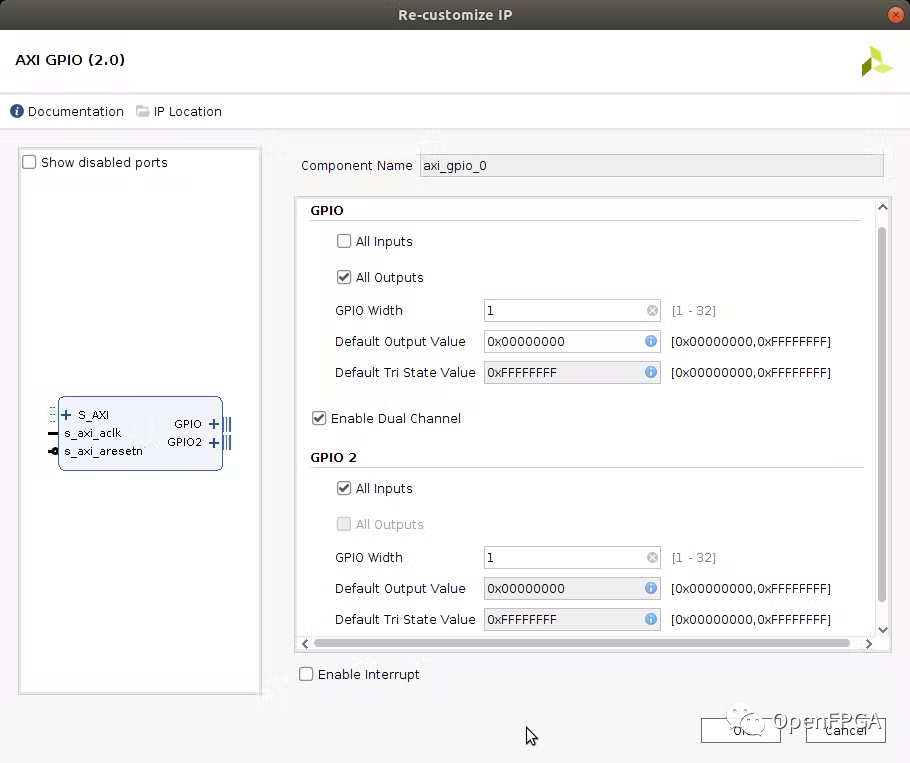

为了给触发器提供源,我添加了一个 AXI GPIO IP ,其中第一个通道作为输出,第二个通道作为输入。自动连接即可。

为 AXI GPIO 模块运行自动连接后,将输出 GPIO 通道连接到触发器的 d_in,将触发器的 q_out 连接到输入 GPIO 通道。

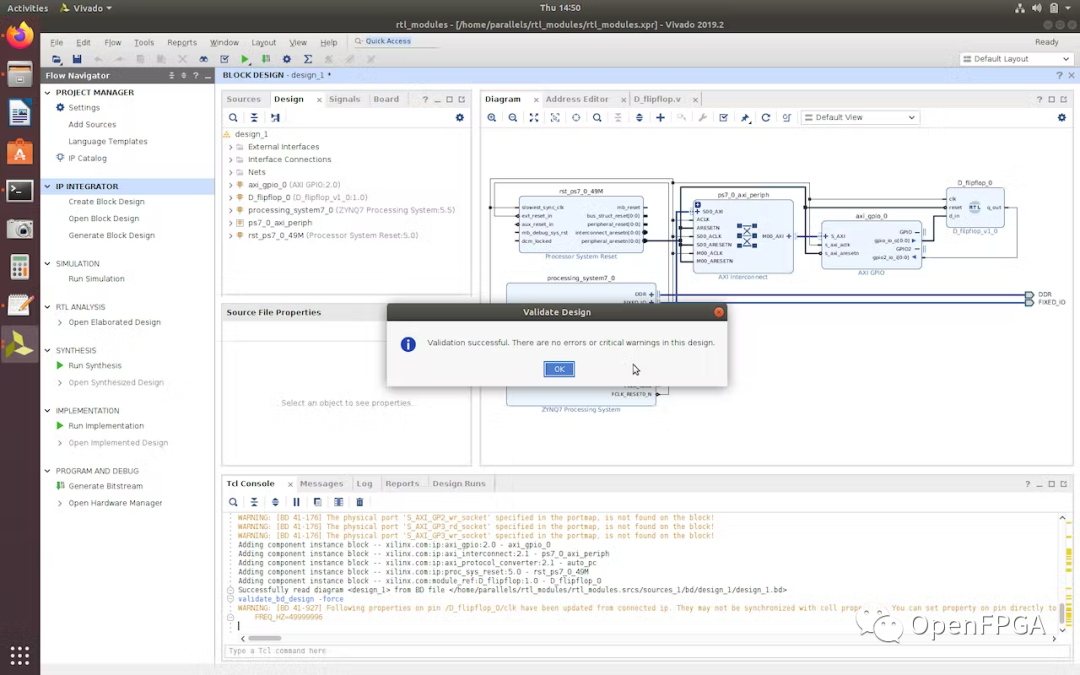

全部连接好后,点击那个勾勾进行验证。

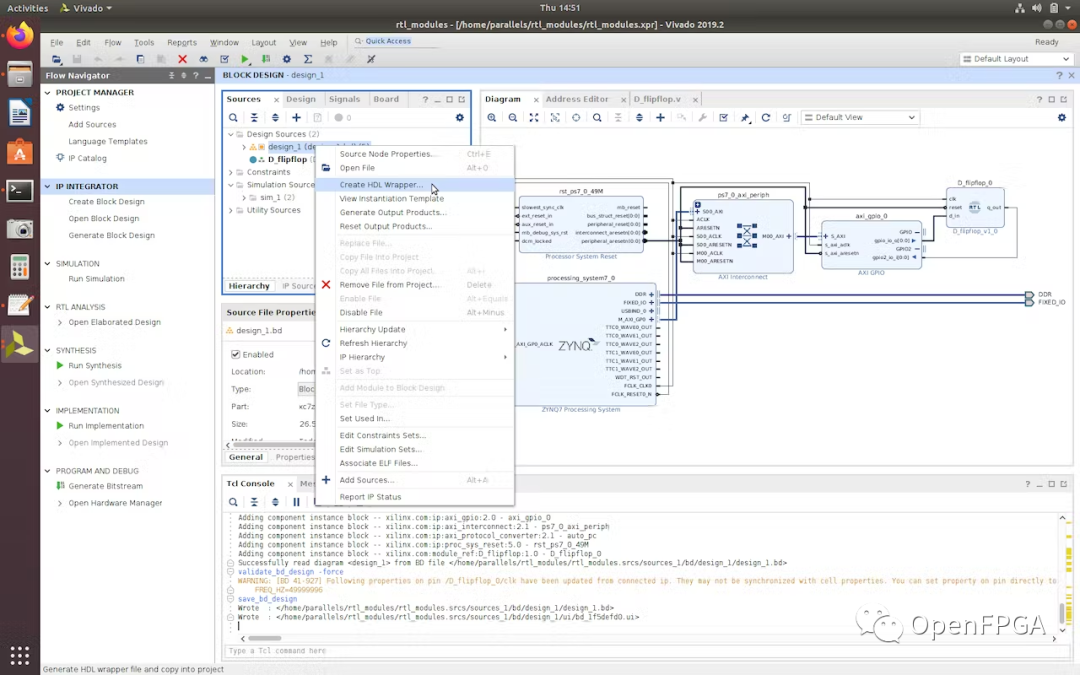

Block Design完成后,为Block Design生成顶层文件。

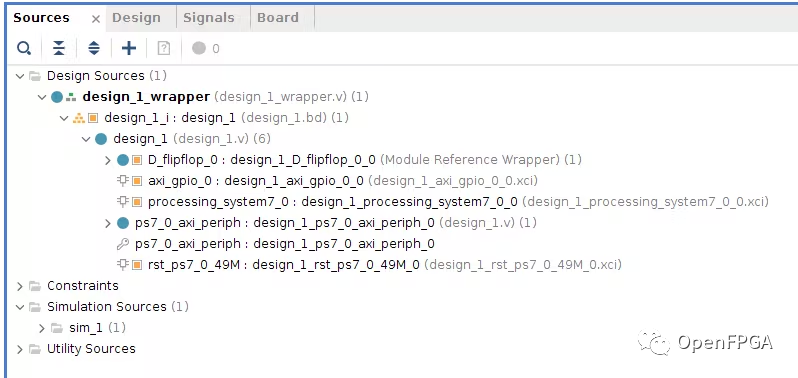

完成后可以看下整个项目的文件层次结构。

就是这样,OVER~