版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_41754003/article/details/113407158

处理器系统与可编程逻辑的接口

如前所述,Zynq 的表现不仅仅依赖于它的两个组成部分 PS 和 PL 的特性,还在于能把两者协同起来形成完整、集成的系统的能力。这其中起关键作用的,是一组高度定制的 AXI 互联和接口用来在两个部分之间形成桥梁。另外,在 PS 和 PL 之间还有一些其他类型的连接,特别是 EMIO。本节讨论 PS 和 PL 之间的连接,并探讨如何使用这些连接。我们从介绍 AXI 标准开始,这是大多数连接的基础。

AXI 标准

AXI 表示的是高级可扩展接口(Advanced eXtensible Interface),当前的版本是 AXI4,它是 ARM AMBA®3.0 开放标准的一部分。第三方厂家生产的许多芯片和IP 包都是基于这个标准的。AMBA 标准原本是 ARM 开发用于单片机的,第一版是 1996 年发布的。自那之后,标准被修订和扩展过,现在 ARM 描述它是 “ 片上通讯的事实标准 ”。现在它主要用于片上系统,包括基于 FPGA 的 SoC,或是 Zynq 这样的包含了 FPGA 部分的芯片。实际上,Xilinx 做了很大的贡献来把 AXI4 定义为 FPGA 架构内使用的优化的互联技术。

在 ISE® Design Suite 的 12.3 版中,Xilinx 工具链第一次引入了对 AXI 的支持,现在在 Vivado Design Suite 中有了进一步的支持。AXI 总线可以灵活使用,而且一般情况下是用来在一个嵌入式系统中连接处理器和其他 IP 包的。实际上有三类 AXI4,每一类代表了一种不同的总线协议,下面会有总结。对于一个特定的连接选择哪个 AXI 总线协议是基于那个连接所需的特性的。

• AXI4 — 用于存储映射链接,它支持最高的性能:通过一簇高达 256 个数据字 (或 “ 数据拍 (data beats)”)的数据传输来给定一个地址。

• AXI4-Lite — 一种简化了的链接,只支持每次连接传输一个数据(非批量)。AXI4-Lite也是存储映射的:这种协议下每次传输一个地址和单个数据。

• AXI4-Stream — 用于高速流数据,支持批量传输无限大小的数据。没有地址机制,这种总线类型最适合源和目的地之间的直接数据流 (非存储器映射)。

前面的描述中用到了 “ 存储映射 ” 这个术语,有必要在此简要定义一下它的含义。如果一个协议是存储映射的,那么在主机所发出的会话(无论读或写)中就会标明一个地址,这个地址是对应于系统存储空间中的一个地址的。对于仅支持每次会话单个数据传输的 AXI4-Lite 而言,数据就是写入那个指定的地址,或从那个地址读出;而在 AXI4 批量的情况下,地址表明的是要传输的第一个数据字的地址,而从机端必须计算随后的数据字的地址。

AXI 互联和接口

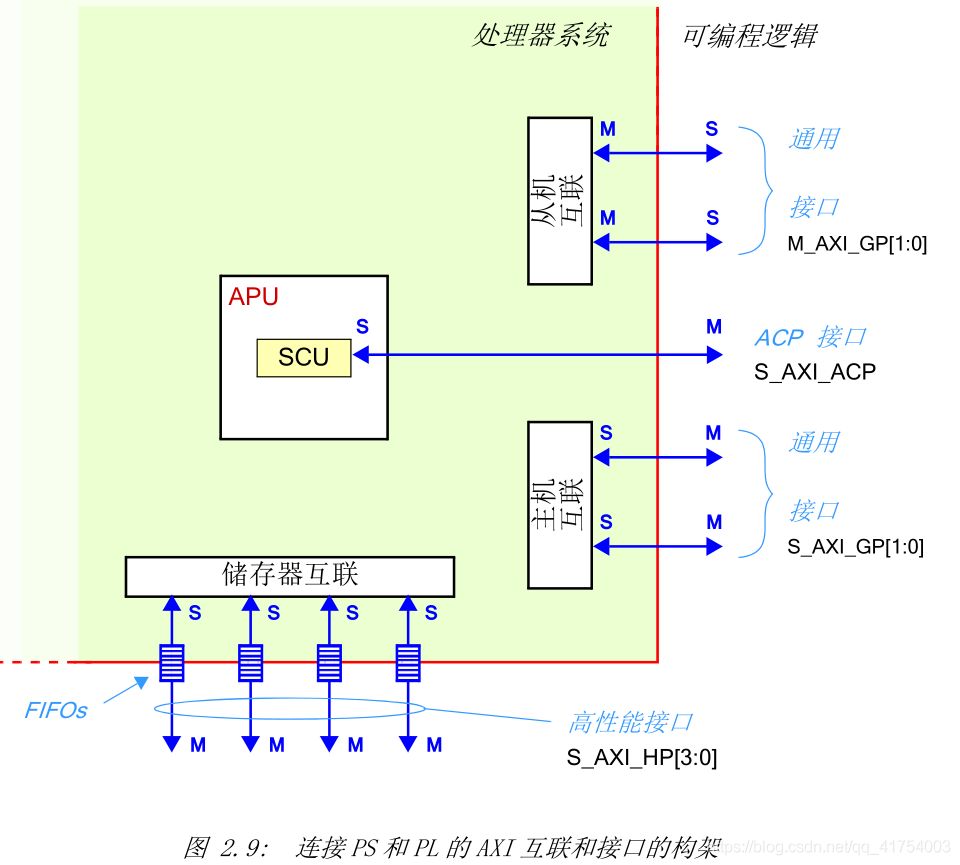

在 PS 和 PL 之间的主要连接是通过一组 9 个 AXI 接口,每个接口有多个通道组成。这些形成了 PS 内部的互联以及与 PL 的连接,如图 2.9 所示。这里,有必要定义两个重要的术语:

• 互联(Interconnect) — 互联实际上是一个开关,管理并直接传递所连接的之间的通信。在 PS 内有几个互联,其中有些还直接连接到 PL(如图2.9),而另一些是只用于内部连接的。这些互联之间的连接也是用 AXI 接口所构成的。

• 接口 (Interface) — 用于在系统内的主机和从机之间传递数据、地址和握手信号的点对点连接。

从图上可以注意到所有的接口都明确地连接到 PS 内的 AXI 互联,唯一例外的是ACP 接口,它直接连到 APU 里面的一致性控制单元 (SCU)。在处理器系统内部,AXI 接口用在 ARM APU 内部 (用来连接处理器核和 SCU、cache 存储器和 OCM),及连接 PS 内的各种互联。这些连接是对 PS-PL 边界上的连接的补充。特别的,图 2.9 所示的三个互联(存储器、主机和从机互联)是内部连接到中央互联 (Central Interconnect)的,图中没有画出这个互联,但是在图2.2 上可以看到。PS 内部连接的全部细节,包括表达所有 AXI 互联和接口的框图。

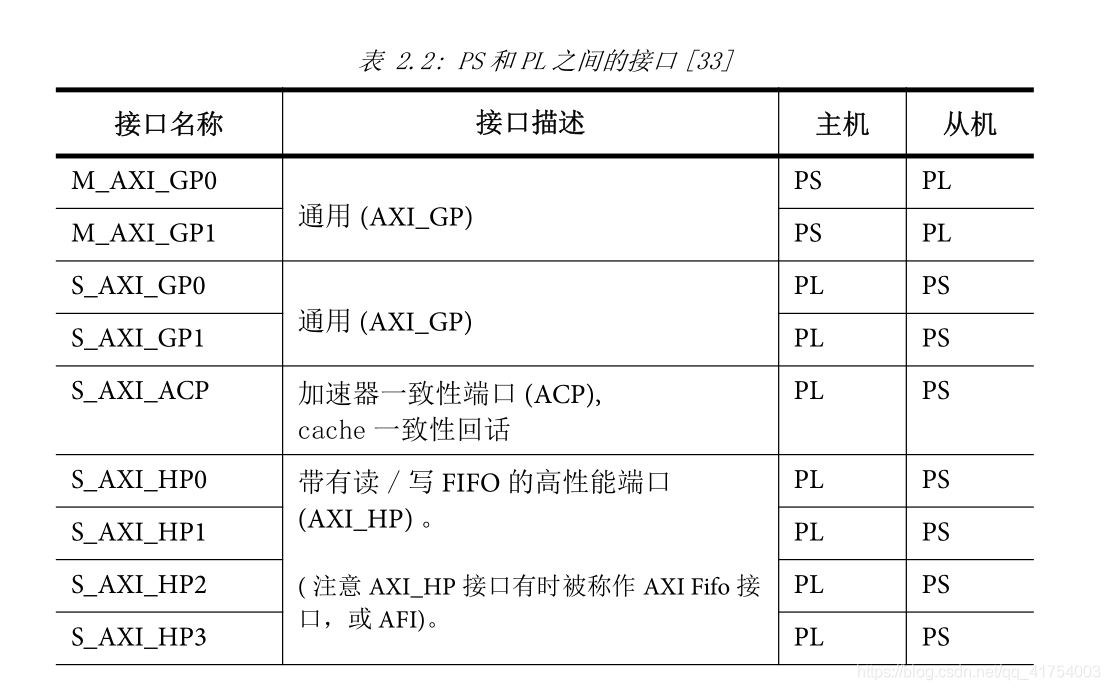

表 2.2 给出了图 2.9 中的箭头所表示的接口的总结。它给出了每个接口的简述,标出了主机和从机(按照惯例,主机是控制总线并发起会话的,而从机是做响应的)。注意接口命名的规范(在表 2.2 的第一列)是表示了 PS 的角色的,也就是说,第一个字母 “M” 表示 PS 是主机,而第一个字母 “S” 表示 PS 是从机。

进一步解释这些不同类型的 PS-PL AXI 接口的作用:

• 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。

• 加速器一致性端口(Accelerator Coherency Port) — 在 PL 和 APU 内的 SCU之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL的单元之间的一致性。PL 是做主机的。

• 高性能端口(High Performance Ports) — 四个高性能 AXI 接口,带有 FIFO缓冲来提供 “ 批量 ” 读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在所有四个接口中 PL 都是做主机的。

本文关于AIX介绍摘自《the zynq book》,具体如何使用可参照官方文档ug761